Vol. 3B 18-25

PERFORMANCE MONITORING

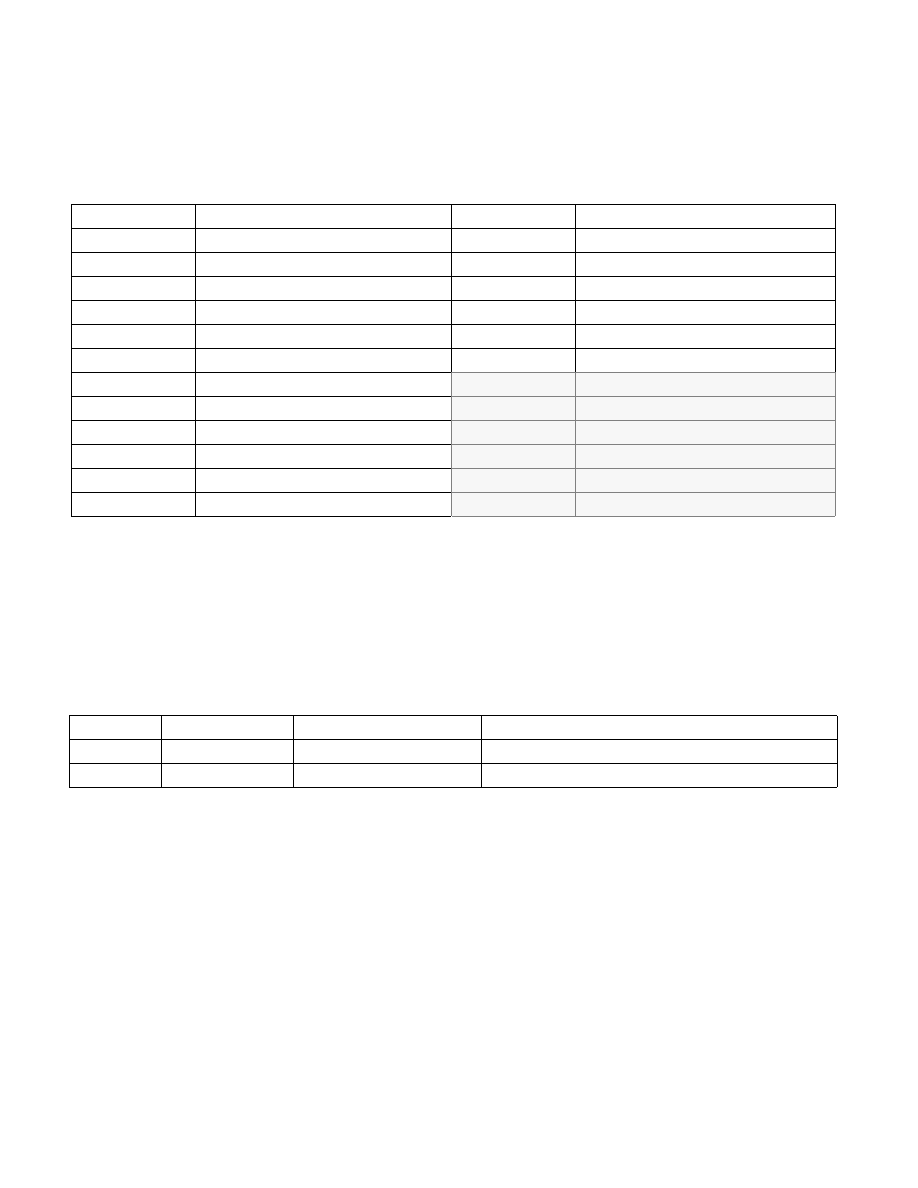

PEBS Record Format The PEBS record format supported by processors based on the Intel Silvermont microarchi-

tecture is shown in Table 18-13, and each field in the PEBS record is 64 bits long.

18.6.2

Offcore Response Event

Event number 0B7H support offcore response monitoring using an associated configuration MSR,

MSR_OFFCORE_RSP0 (address 1A6H) in conjunction with umask value 01H or MSR_OFFCORE_RSP1 (address

1A7H) in conjunction with umask value 02H. Table 18-14 lists the event code, mask value and additional off-core

configuration MSR that must be programmed to count off-core response events using IA32_PMCx.

In the Silvermont microarchitecture, each MSR_OFFCORE_RSPx is shared by two processor cores.

The layout of MSR_OFFCORE_RSP0 and MSR_OFFCORE_RSP1 are shown in Figure 18-18 and Figure 18-19. Bits

15:0 specifies the request type of a transaction request to the uncore. Bits 30:16 specifies supplier information,

bits 37:31 specifies snoop response information.

Additionally, MSR_OFFCORE_RSP0 provides bit 38 to enable measurement of average latency of specific type of

offcore transaction requests using two programmable counter simultaneously, see Section 18.6.3 for details.

Table 18-13. PEBS Record Format for the Silvermont Microarchitecture

Byte Offset

Field

Byte Offset

Field

00H

R/EFLAGS

60H

R10

08H

R/EIP

68H

R11

10H

R/EAX

70H

R12

18H

R/EBX

78H

R13

20H

R/ECX

80H

R14

28H

R/EDX

88H

R15

30H

R/ESI

90H

IA32_PERF_GLOBAL_STATUS

38H

R/EDI

98H

Reserved

40H

R/EBP

A0H

Reserved

48H

R/ESP

A8H

Reserved

50H

R8

B0H

EventingRIP

58H

R9

B8H

Reserved

Table 18-14. OffCore Response Event Encoding

Counter

Event code

UMask

Required Off-core Response MSR

PMC0-1

B7H

01H

MSR_OFFCORE_RSP0 (address 1A6H)

PMC0-1

B7H

02H

MSR_OFFCORE_RSP1 (address 1A7H)