27-4 Vol. 3C

VM EXITS

27.2

RECORDING VM-EXIT INFORMATION AND UPDATING VM-ENTRY CONTROL

FIELDS

VM exits begin by recording information about the nature of and reason for the VM exit in the VM-exit information

fields. Section 27.2.1 to Section 27.2.4 detail the use of these fields.

In addition to updating the VM-exit information fields, the valid bit (bit 31) is cleared in the VM-entry interruption-

information field. If bit 5 of the IA32_VMX_MISC MSR (index 485H) is read as 1 (see Appendix A.6), the value of

IA32_EFER.LMA is stored into the “IA-32e mode guest” VM-entry control.

1

27.2.1

Basic VM-Exit Information

Section 24.9.1 defines the basic VM-exit information fields. The following items detail their use.

•

Exit reason.

— Bits 15:0 of this field contain the basic exit reason. It is loaded with a number indicating the general cause

of the VM exit. Appendix C lists the numbers used and their meaning.

— Bit 27 of this field is set to 1 if the VM exit occurred while the logical processor was in enclave mode.

Such VM exits includes those caused by interrupts, non-maskable interrupts, system-management

interrupts, INIT signals, and exceptions occurring in enclave mode as well as exceptions encountered

during the delivery of such events incident to enclave mode.

A VM exit also sets this bit if it is incident to delivery of an event injected by VM entry and the guest inter-

ruptibility-state field indicates an enclave interrupt (bit 4 of the field is 1).

— The remainder of the field (bits 31:28 and bits 26:16) is cleared to 0 (certain SMM VM exits may set some

of these bits; see Section 34.15.2.3).

2

•

Exit qualification. This field is saved for VM exits due to the following causes: debug exceptions; page-fault

exceptions; start-up IPIs (SIPIs); system-management interrupts (SMIs) that arrive immediately after the

retirement of I/O instructions; task switches; INVEPT; INVLPG; INVPCID; INVVPID; LGDT; LIDT; LLDT; LTR;

SGDT; SIDT; SLDT; STR; VMCLEAR; VMPTRLD; VMPTRST; VMREAD; VMWRITE; VMXON; XRSTORS; XSAVES;

control-register accesses; MOV DR; I/O instructions; MWAIT; accesses to the APIC-access page (see Section

29.4); EPT violations; EOI virtualization (see Section 29.1.4); APIC-write emulation (see Section 29.4.3.3);

and page-modification log full (see Section 28.2.5). For all other VM exits, this field is cleared. The following

items provide details:

— For a debug exception, the exit qualification contains information about the debug exception. The

information has the format given in Table 27-1.

1. Bit 5 of the IA32_VMX_MISC MSR is read as 1 on any logical processor that supports the 1-setting of the “unrestricted guest” VM-

execution control.

2. Bit 31 of this field is set on certain VM-entry failures; see Section 26.7.

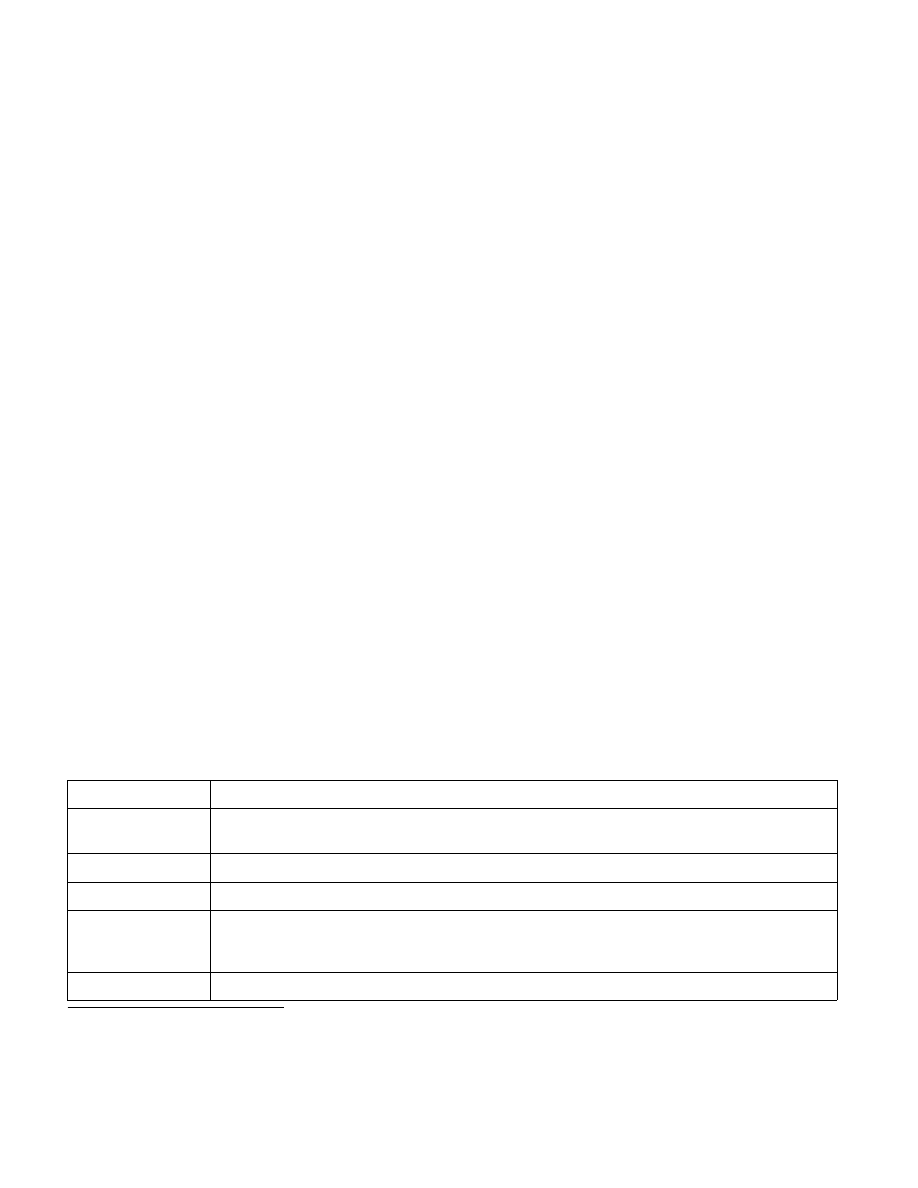

Table 27-1. Exit Qualification for Debug Exceptions

Bit Position(s)

Contents

3:0

B3 – B0. When set, each of these bits indicates that the corresponding breakpoint condition was met. Any of

these bits may be set even if its corresponding enabling bit in DR7 is not set.

12:4

Reserved (cleared to 0).

13

BD. When set, this bit indicates that the cause of the debug exception is “debug register access detected.”

14

BS. When set, this bit indicates that the cause of the debug exception is either the execution of a single

instruction (if RFLAGS.TF = 1 and IA32_DEBUGCTL.BTF = 0) or a taken branch (if

RFLAGS.TF = DEBUGCTL.BTF = 1).

63:15

Reserved (cleared to 0). Bits 63:32 exist only on processors that support Intel 64 architecture.