Vol. 3B 19-33

PERFORMANCE-MONITORING EVENTS

19.4.1 Performance Monitoring Events in the Processor Core of Intel Xeon Processor E5 v3

Family

Non-architectural performance monitoring events in the processor core that are applicable only to Intel Xeon

processor E5 v3 family based on the Haswell-E microarchitecture, with CPUID signature of

DisplayFamily_DisplayModel 06_3FH, are listed in Table 19-10. The performance events listed in Table 19-7 and

Table 19-8 also apply Intel Xeon processor E5 v3 family, except that the OFF_CORE_RESPONSE_x event listed in

Table 19-7 should reference Table 18-50.

Uncore performance monitoring events for Intel Xeon Processor E5 v3 families are described in “Intel® Xeon®

Processor E5 v3 Uncore Performance Monitoring Programming Reference Manual”.

19.5

PERFORMANCE MONITORING EVENTS FOR 3RD GENERATION

INTEL

®

CORE

™

PROCESSORS

3rd generation Intel

®

Core™ processors and Intel Xeon processor E3-1200 v2 product family are based on Intel

microarchitecture code name Ivy Bridge. They support architectural performance-monitoring events listed in Table

19-1. Non-architectural performance-monitoring events in the processor core are listed in Table 19-11. The events

in Table 19-11 apply to processors with CPUID signature of DisplayFamily_DisplayModel encoding with the

following values: 06_3AH. Fixed counters in the core PMU support the architecture events defined in Table 19-22.

Additional information on event specifics (e.g. derivative events using specific IA32_PERFEVTSELx modifiers, limi-

tations, special notes and recommendations) can be found at http://software.intel.com/en-us/forums/software-

tuning-performance-optimization-platform-monitoring.

83H

01H

UNC_ARB_COH_TRK_OCCUPA

NCY.ALL

Cycles weighted by number of requests pending in

Coherency Tracker.

Counter 0 only.

84H

01H

UNC_ARB_COH_TRK_REQUES

T.ALL

Number of requests allocated in Coherency Tracker.

NOTES:

1. The uncore events must be programmed using MSRs located in specific performance monitoring units in the uncore. UNC_CBO*

events are supported using MSR_UNC_CBO* MSRs; UNC_ARB* events are supported using MSR_UNC_ARB*MSRs.

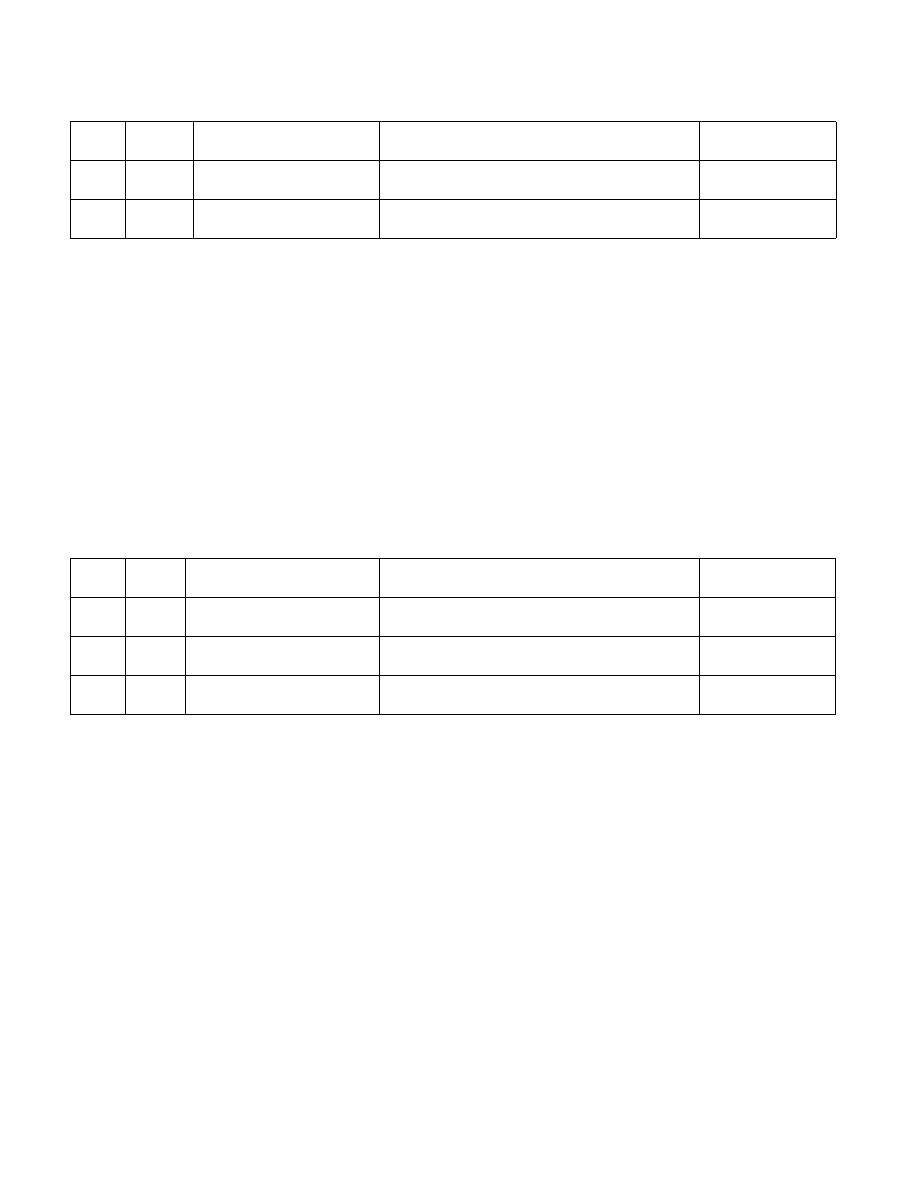

Table 19-10. Non-Architectural Performance Events Applicable only to the Processor Core of

Intel® Xeon® Processor E5 v3 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

D3H

04H

MEM_LOAD_UOPS_L3_MISS_RE

TIRED.REMOTE_DRAM

Retired load uops whose data sources were remote

DRAM (snoop not needed, Snoop Miss).

Supports PEBS.

D3H

10H

MEM_LOAD_UOPS_L3_MISS_RE

TIRED.REMOTE_HITM

Retired load uops whose data sources were remote

cache HITM.

Supports PEBS.

D3H

20H

MEM_LOAD_UOPS_L3_MISS_RE

TIRED.REMOTE_FWD

Retired load uops whose data sources were forwards

from a remote cache.

Supports PEBS.

Table 19-9. Non-Architectural Uncore Performance Events in the 4th Generation Intel® Core™ Processors (Contd.)

Event

Num.

1

Umask

Value

Event Mask Mnemonic

Description

Comment