Vol. 3B 19-21

PERFORMANCE-MONITORING EVENTS

19.4

PERFORMANCE MONITORING EVENTS FOR THE 4TH GENERATION

INTEL

®

CORE

™

PROCESSORS

4th generation Intel

®

Core™ processors and Intel Xeon processor E3-1200 v3 product family are based on the

Haswell microarchitecture. They support the architectural performance-monitoring events listed in Table 19-1.

Non-architectural performance-monitoring events in the processor core are listed in Table 19-7. The events in

Table 19-7 apply to processors with CPUID signature of DisplayFamily_DisplayModel encoding with the following

values: 06_3CH, 06_45H and 06_46H. Table 19-8 lists performance events focused on supporting Intel TSX (see

Section 18.11.5). Fixed counters in the core PMU support the architecture events defined in Table 19-2.

Additional information on event specifics (e.g., derivative events using specific IA32_PERFEVTSELx modifiers, limi-

tations, special notes and recommendations) can be found at http://software.intel.com/en-us/forums/software-

tuning-performance-optimization-platform-monitoring.

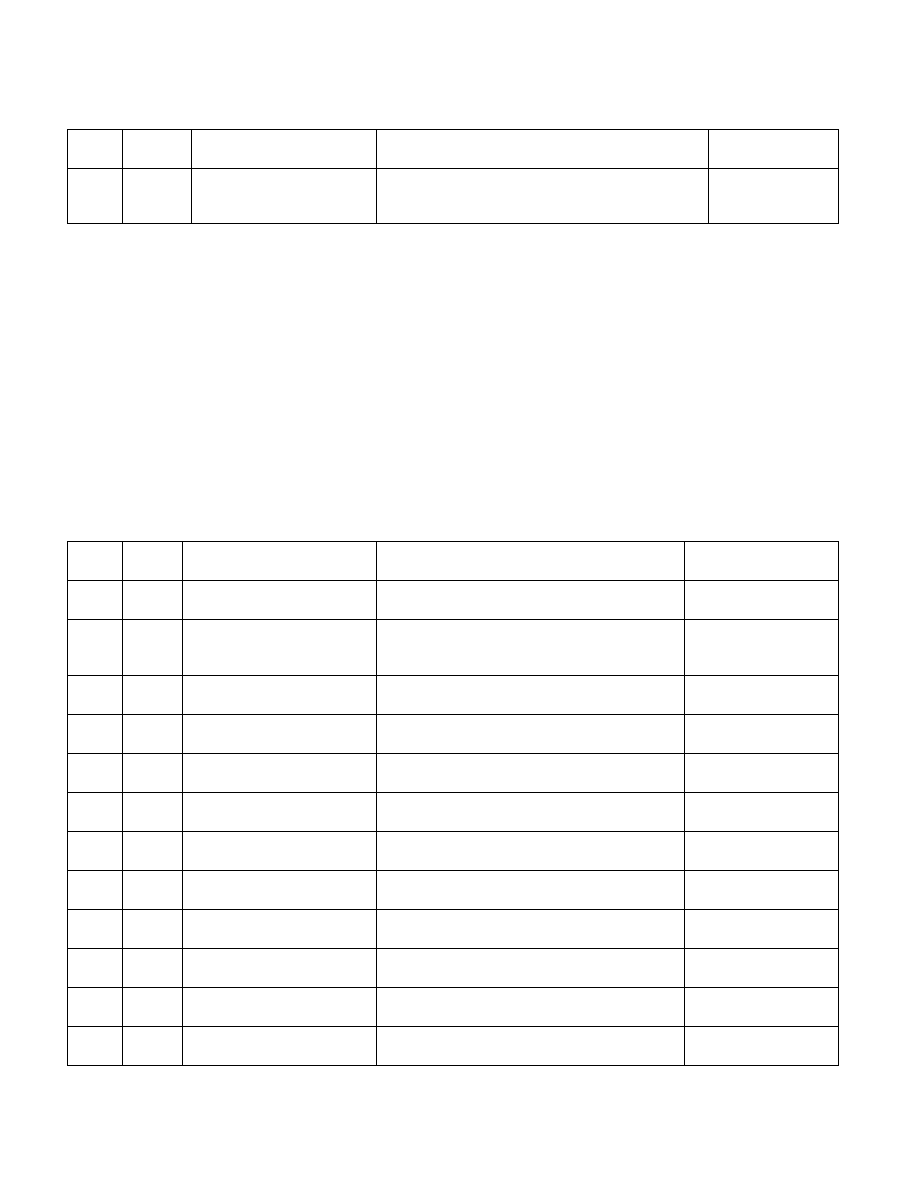

Table 19-6. Intel® TSX Performance Event Addendum in Processors Based on Broadwell Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

54H

02H

TX_MEM.ABORT_CAPACITY

Number of times a transactional abort was signaled due

to a data capacity limitation for transactional reads or

writes.

Table 19-7. Non-Architectural Performance Events in the Processor Core of

4th Generation Intel® Core™ Processors

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

03H

02H

LD_BLOCKS.STORE_FORWARD

Loads blocked by overlapping with store buffer that

cannot be forwarded.

03H

08H

LD_BLOCKS.NO_SR

The number of times that split load operations are

temporarily blocked because all resources for

handling the split accesses are in use.

05H

01H

MISALIGN_MEM_REF.LOADS

Speculative cache-line split load uops dispatched to

L1D.

05H

02H

MISALIGN_MEM_REF.STORES

Speculative cache-line split store-address uops

dispatched to L1D.

07H

01H

LD_BLOCKS_PARTIAL.ADDRESS

_ALIAS

False dependencies in MOB due to partial compare

on address.

08H

01H

DTLB_LOAD_MISSES.MISS_CAUS

ES_A_WALK

Misses in all TLB levels that cause a page walk of any

page size.

08H

02H

DTLB_LOAD_MISSES.WALK_COM

PLETED_4K

Completed page walks due to demand load misses

that caused 4K page walks in any TLB levels.

08H

04H

DTLB_LOAD_MISSES.WALK_COM

PLETED_2M_4M

Completed page walks due to demand load misses

that caused 2M/4M page walks in any TLB levels.

08H

0EH

DTLB_LOAD_MISSES.WALK_COM

PLETED

Completed page walks in any TLB of any page size

due to demand load misses.

08H

10H

DTLB_LOAD_MISSES.WALK_DUR

ATION

Cycle PMH is busy with a walk.

08H

20H

DTLB_LOAD_MISSES.STLB_HIT_

4K

Load misses that missed DTLB but hit STLB (4K).

08H

40H

DTLB_LOAD_MISSES.STLB_HIT_

2M

Load misses that missed DTLB but hit STLB (2M).