19-30 Vol. 3B

PERFORMANCE-MONITORING EVENTS

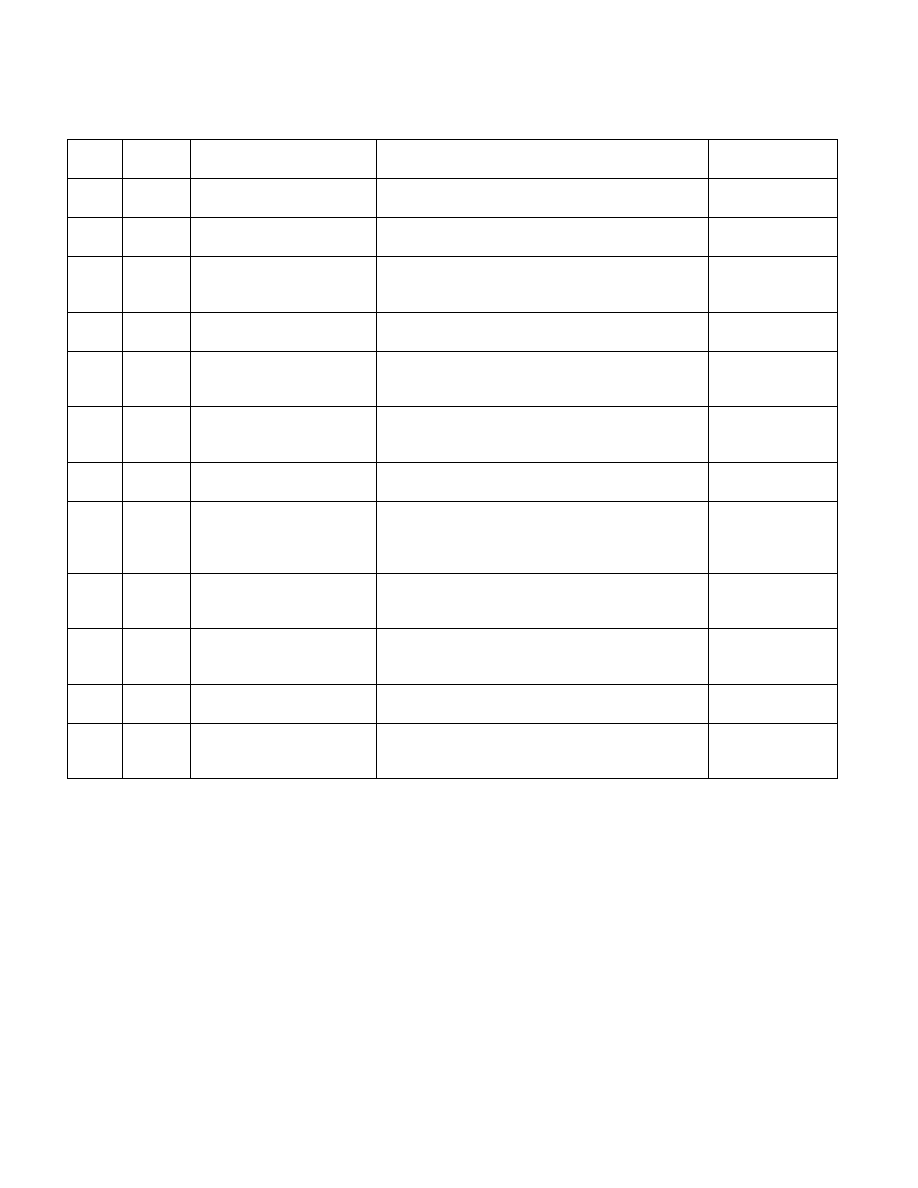

Table 19-8. Intel TSX Performance Events in Processors Based on Haswell Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

54H

01H

TX_MEM.ABORT_CONFLICT

Number of times a transactional abort was signaled due

to a data conflict on a transactionally accessed address.

54H

02H

TX_MEM.ABORT_CAPACITY_W

RITE

Number of times a transactional abort was signaled due

to a data capacity limitation for transactional writes.

54H

04H

TX_MEM.ABORT_HLE_STORE_

TO_ELIDED_LOCK

Number of times a HLE transactional region aborted due

to a non XRELEASE prefixed instruction writing to an

elided lock in the elision buffer.

54H

08H

TX_MEM.ABORT_HLE_ELISION

_BUFFER_NOT_EMPTY

Number of times an HLE transactional execution aborted

due to NoAllocatedElisionBuffer being non-zero.

54H

10H

TX_MEM.ABORT_HLE_ELISION

_BUFFER_MISMATCH

Number of times an HLE transactional execution aborted

due to XRELEASE lock not satisfying the address and

value requirements in the elision buffer.

54H

20H

TX_MEM.ABORT_HLE_ELISION

_BUFFER_UNSUPPORTED_ALI

GNMENT

Number of times an HLE transactional execution aborted

due to an unsupported read alignment from the elision

buffer.

54H

40H

TX_MEM.HLE_ELISION_BUFFE

R_FULL

Number of times HLE lock could not be elided due to

ElisionBufferAvailable being zero.

5DH

01H

TX_EXEC.MISC1

Counts the number of times a class of instructions that

may cause a transactional abort was executed. Since this

is the count of execution, it may not always cause a

transactional abort.

5DH

02H

TX_EXEC.MISC2

Counts the number of times a class of instructions (for

example, vzeroupper) that may cause a transactional

abort was executed inside a transactional region.

5DH

04H

TX_EXEC.MISC3

Counts the number of times an instruction execution

caused the transactional nest count supported to be

exceeded.

5DH

08H

TX_EXEC.MISC4

Counts the number of times an XBEGIN instruction was

executed inside an HLE transactional region.

5DH

10H

TX_EXEC.MISC5

Counts the number of times an instruction with HLE-

XACQUIRE semantic was executed inside an RTM

transactional region.