Vol. 3B 19-117

PERFORMANCE-MONITORING EVENTS

Processors based on the Enhanced Intel Core microarchitecture support the architectural and non-architectural

performance-monitoring events listed in Table 19-1 and Table 19-23. In addition, they also support the following

non-architectural performance-monitoring events listed in Table 19-21. Fixed counters support the architecture

events defined in Table 19-22.

19.10 PERFORMANCE MONITORING EVENTS FOR INTEL

®

XEON

®

PROCESSOR

3000, 3200, 5100, 5300 SERIES AND INTEL

®

CORE

™

2

DUO PROCESSORS

Processors based on the Intel

®

Core™ microarchitecture support architectural and non-architectural performance-

monitoring events.

Fixed-function performance counters are introduced first on processors based on Intel Core microarchitecture.

Table 19-22 lists pre-defined performance events that can be counted using fixed-function performance counters.

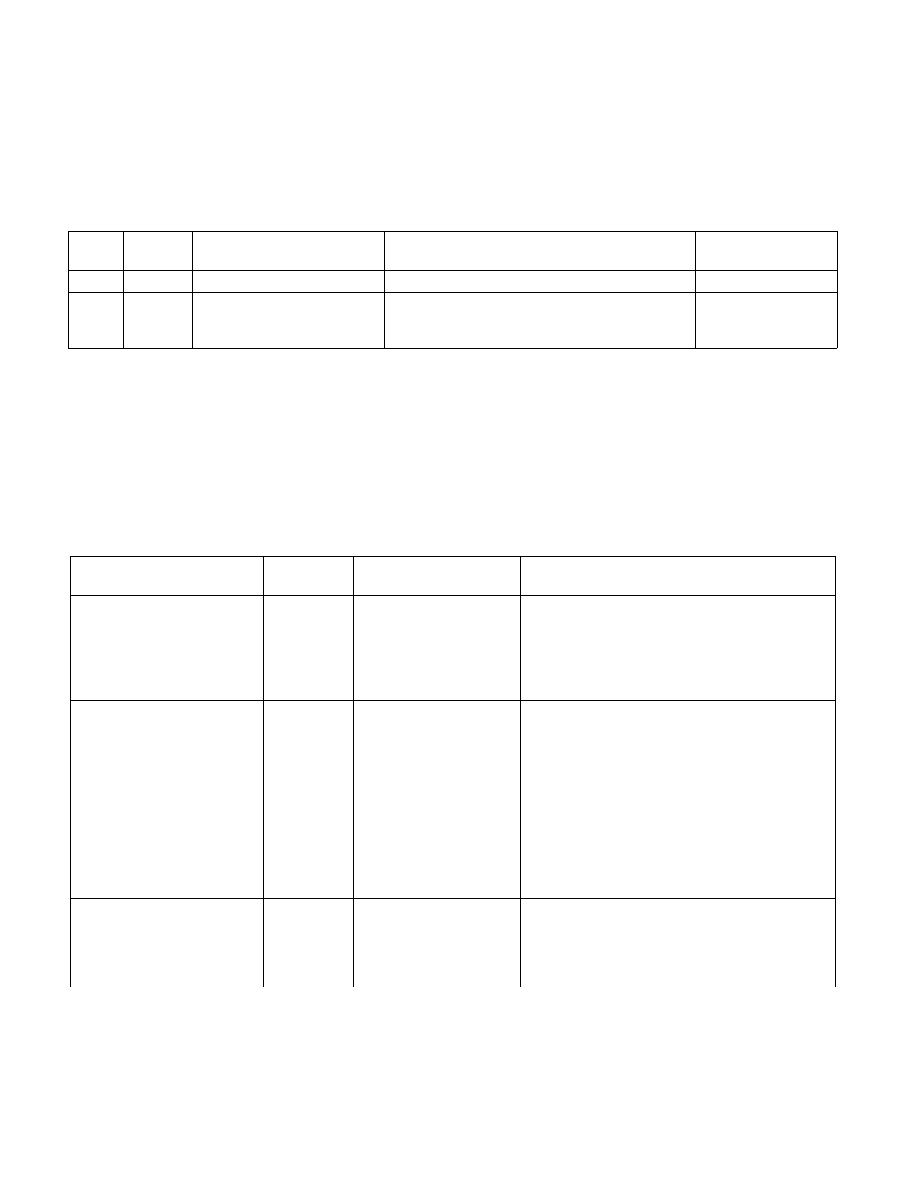

Table 19-21. Non-Architectural Performance Events for Processors Based on Enhanced Intel Core

Microarchitecture

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

C0H

08H

INST_RETIRED.VM_HOST

Instruction retired while in VMX root operations.

D2H

10H

RAT_STAALS.OTHER_SERIALIZ

ATION_STALLS

This event counts the number of stalls due to other

RAT resource serialization not counted by Umask

value 0FH.

Table 19-22. Fixed-Function Performance Counter and Pre-defined Performance Events

Fixed-Function Performance

Counter

Address

Event Mask Mnemonic

Description

MSR_PERF_FIXED_

CTR0/IA32_PERF_FIXED_CTR0

309H

Inst_Retired.Any

This event counts the number of instructions that

retire execution. For instructions that consist of

multiple micro-ops, this event counts the retirement

of the last micro-op of the instruction. The counter

continues counting during hardware interrupts, traps,

and inside interrupt handlers.

MSR_PERF_FIXED_

CTR1/IA32_PERF_FIXED_CTR1

30AH

CPU_CLK_UNHALTED.CORE This event counts the number of core cycles while the

core is not in a halt state. The core enters the halt

state when it is running the HLT instruction. This

event is a component in many key event ratios.

The core frequency may change from time to time

due to transitions associated with Enhanced Intel

SpeedStep Technology or TM2. For this reason this

event may have a changing ratio with regards to time.

When the core frequency is constant, this event can

approximate elapsed time while the core was not in

halt state.

MSR_PERF_FIXED_

CTR2/IA32_PERF_FIXED_CTR2

30BH

CPU_CLK_UNHALTED.REF

This event counts the number of reference cycles

when the core is not in a halt state and not in a TM

stop-clock state. The core enters the halt state when

it is running the HLT instruction or the MWAIT

instruction.