Vol. 3B 18-89

PERFORMANCE MONITORING

18.15.4 Debug Store (DS) Mechanism

The debug store (DS) mechanism was introduced with processors based on Intel NetBurst microarchitecture to

allow various types of information to be collected in memory-resident buffers for use in debugging and tuning

programs. The DS mechanism can be used to collect two types of information: branch records and processor

event-based sampling (PEBS) records. The availability of the DS mechanism in a processor is indicated with the DS

feature flag (bit 21) returned by the CPUID instruction.

See Section 17.4.5, ŌĆ£Branch Trace Store (BTS),ŌĆØ and Section 18.15.7, ŌĆ£Processor Event-Based Sampling (PEBS),ŌĆØ

for a description of these facilities. Records collected with the DS mechanism are saved in the DS save area. See

Section 17.4.9, ŌĆ£BTS and DS Save Area.ŌĆØ

18.15.5 Programming the Performance Counters

for Non-Retirement Events

The basic steps to program a performance counter and to count events include the following:

1. Select the event or events to be counted.

2. For each event, select an ESCR that supports the event using the values in the ESCR restrictions row in Table

3. Match the CCCR Select value and ESCR name in Table 19-28 to a value listed in Table 18-63; select a CCCR and

performance counter.

4. Set up an ESCR for the specific event or events to be counted and the privilege levels at which the are to be

counted.

5. Set up the CCCR for the performance counter by selecting the ESCR and the desired event filters.

6. Set up the CCCR for optional cascading of event counts, so that when the selected counter overflows its

alternate counter starts.

7. Set up the CCCR to generate an optional performance monitor interrupt (PMI) when the counter overflows. If

PMI generation is enabled, the local APIC must be set up to deliver the interrupt to the processor and a handler

for the interrupt must be in place.

8. Enable the counter to begin counting.

18.15.5.1 Selecting Events to Count

Table 19-29 in Chapter 19 lists a set of at-retirement events for processors based on Intel NetBurst microarchitec-

ture. For each event listed in Table 19-29, setup information is provided. Table 18-64 gives an example of one of

the events.

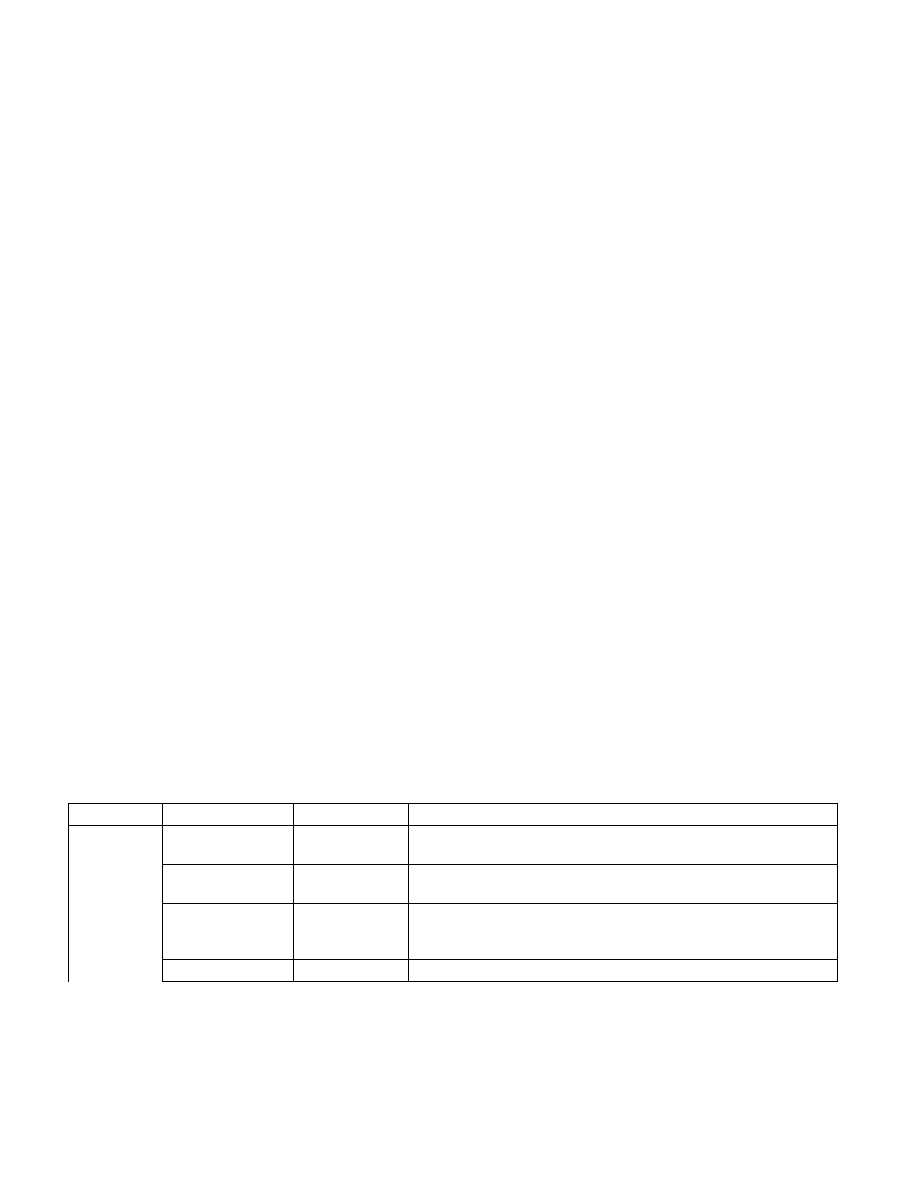

Table 18-64. Event Example

Event Name

Event Parameters

Parameter Value Description

branch_retired

Counts the retirement of a branch. Specify one or more mask bits to select

any combination of branch taken, not-taken, predicted and mispredicted.

ESCR restrictions

MSR_CRU_ESCR2

MSR_CRU_ESCR3

See Table 15-3 for the addresses of the ESCR MSRs.

Counter numbers per

ESCR

ESCR2: 12, 13, 16

ESCR3: 14, 15, 17

The counter numbers associated with each ESCR are provided. The

performance counters and corresponding CCCRs can be obtained from

Table 15-3.

ESCR Event Select

06H

ESCR[31:25]