18-82 Vol. 3B

PERFORMANCE MONITORING

18.15 PERFORMANCE MONITORING (PROCESSORS BASED ON INTEL NETBURST

®

MICROARCHITECTURE)

The performance monitoring mechanism provided in processors based on Intel NetBurst microarchitecture is

different from that provided in the P6 family and Pentium processors. While the general concept of selecting,

filtering, counting, and reading performance events through the WRMSR, RDMSR, and RDPMC instructions is

unchanged, the setup mechanism and MSR layouts are incompatible with the P6 family and Pentium processor

mechanisms. Also, the RDPMC instruction has been extended to support faster reading of counters and to read all

performance counters available in processors based on Intel NetBurst microarchitecture.

The event monitoring mechanism consists of the following facilities:

•

The IA32_MISC_ENABLE MSR, which indicates the availability in an Intel 64 or IA-32 processor of the

performance monitoring and processor event-based sampling (PEBS) facilities.

•

Event selection control (ESCR) MSRs for selecting events to be monitored with specific performance counters.

The number available differs by family and model (43 to 45).

•

18 performance counter MSRs for counting events.

•

18 counter configuration control (CCCR) MSRs, with one CCCR associated with each performance counter.

CCCRs sets up an associated performance counter for a specific method of counting.

•

A debug store (DS) save area in memory for storing PEBS records.

•

The IA32_DS_AREA MSR, which establishes the location of the DS save area.

•

The debug store (DS) feature flag (bit 21) returned by the CPUID instruction, which indicates the availability of

the DS mechanism.

•

The MSR_PEBS_ENABLE MSR, which enables the PEBS facilities and replay tagging used in at-retirement event

counting.

•

A set of predefined events and event metrics that simplify the setting up of the performance counters to count

specific events.

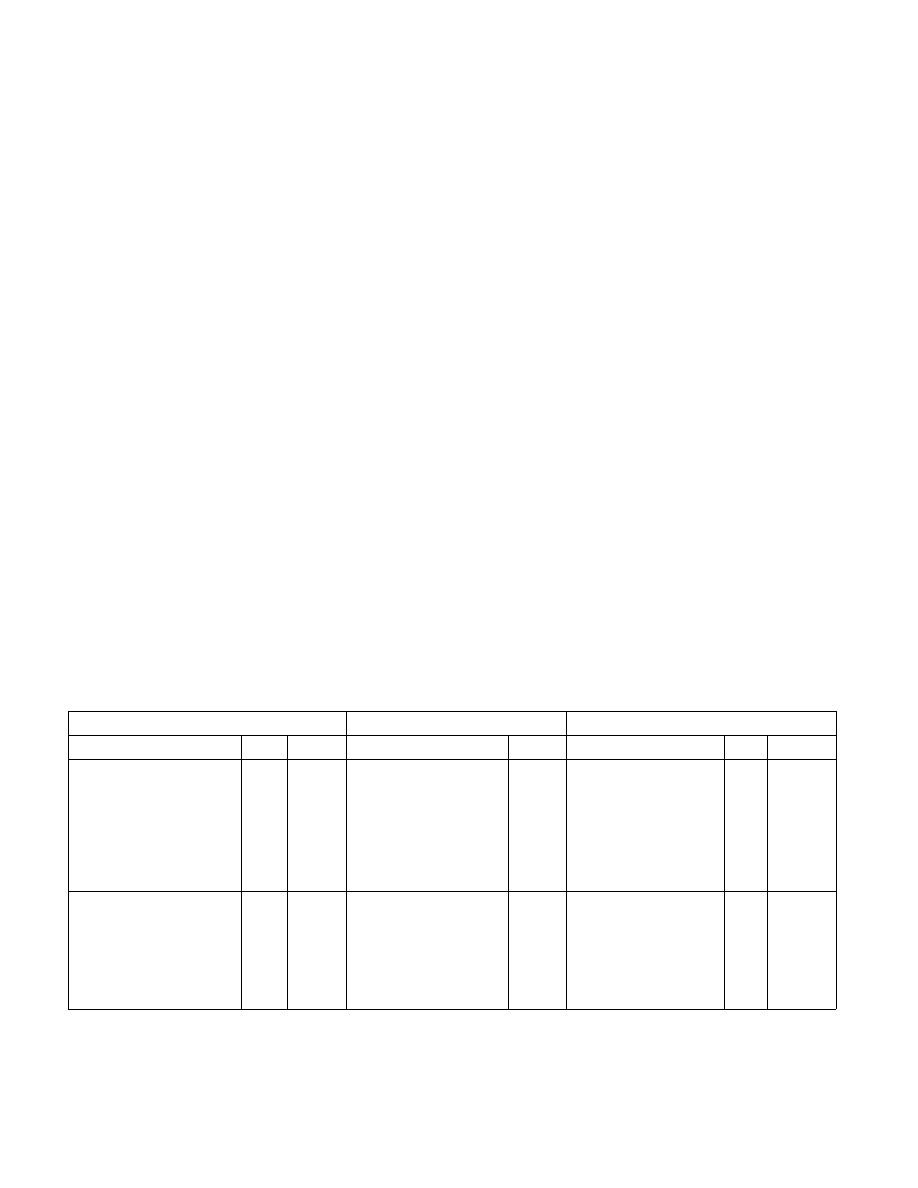

Table 18-63 lists the performance counters and their associated CCCRs, along with the ESCRs that select events to

be counted for each performance counter. Predefined event metrics and events are listed in Chapter 19, “Perfor-

mance-Monitoring Events.”

Table 18-63. Performance Counter MSRs and Associated CCCR and

ESCR MSRs (Processors Based on Intel NetBurst Microarchitecture)

Counter

CCCR

ESCR

Name

No.

Addr

Name

Addr

Name

No.

Addr

MSR_BPU_COUNTER0

0

300H

MSR_BPU_CCCR0

360H

MSR_BSU_ESCR0

MSR_FSB_ESCR0

MSR_MOB_ESCR0

MSR_PMH_ESCR0

MSR_BPU_ESCR0

MSR_IS_ESCR0

MSR_ITLB_ESCR0

MSR_IX_ESCR0

7

6

2

4

0

1

3

5

3A0H

3A2H

3AAH

3ACH

3B2H

3B4H

3B6H

3C8H

MSR_BPU_COUNTER1

1

301H

MSR_BPU_CCCR1

361H

MSR_BSU_ESCR0

MSR_FSB_ESCR0

MSR_MOB_ESCR0

MSR_PMH_ESCR0

MSR_BPU_ESCR0

MSR_IS_ESCR0

MSR_ITLB_ESCR0

MSR_IX_ESCR0

7

6

2

4

0

1

3

5

3A0H

3A2H

3AAH

3ACH

3B2H

3B4H

3B6H

3C8H