Vol. 3B 19-173

PERFORMANCE-MONITORING EVENTS

19.15 PENTIUM

®

4 AND INTEL

®

XEON

®

PROCESSOR PERFORMANCE-

MONITORING EVENTS

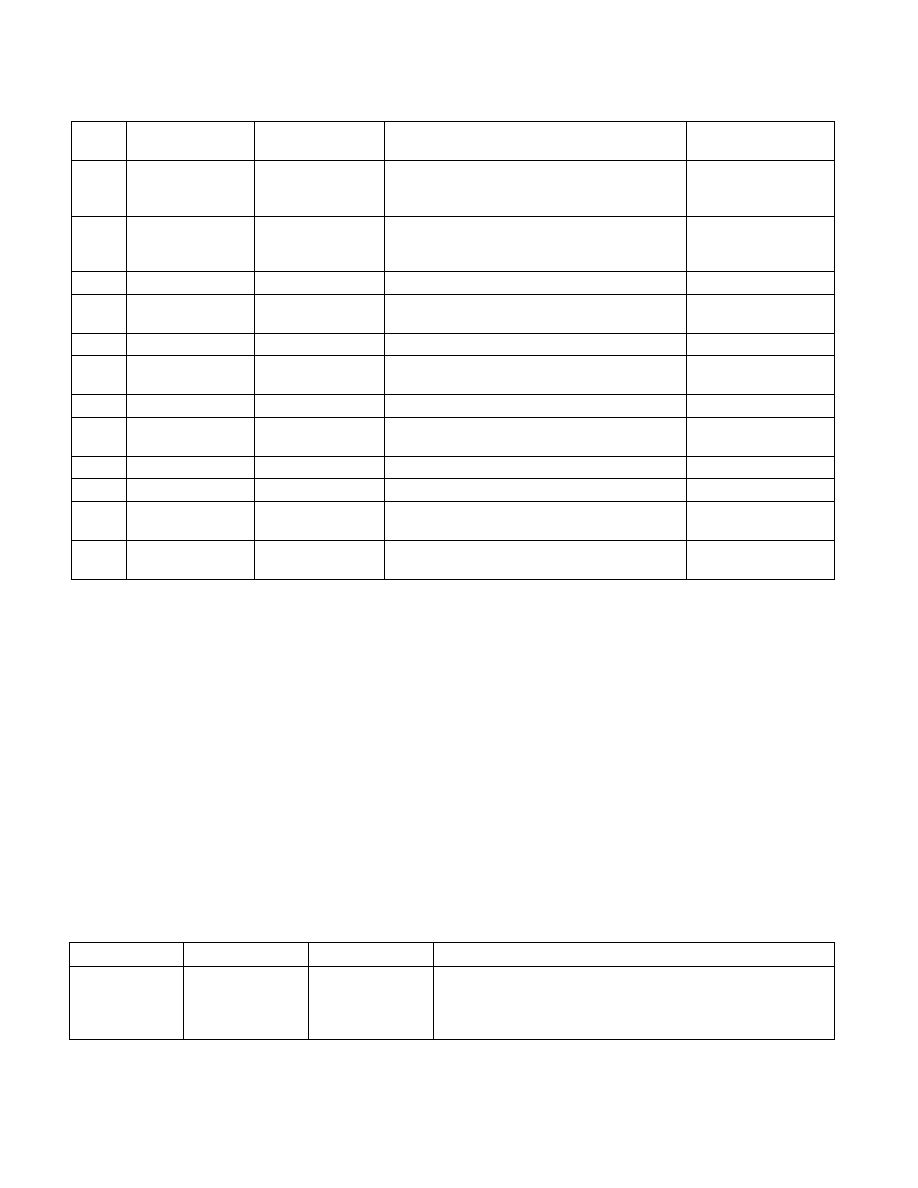

Tables 19-28, 19-29 and 19-30 list performance-monitoring events that can be counted or sampled on processors

based on Intel NetBurst

®

microarchitecture. Table 19-28 lists the non-retirement events, and Table 19-29 lists the

at-retirement events. Tables 19-31, 19-32, and 19-33 describes three sets of parameters that are available for

three of the at-retirement counting events defined in Table 19-29. Table 19-34 shows which of the non-retirement

and at retirement events are logical processor specific (TS) (see Section 18.16.4, “Performance Monitoring

Events”) and which are non-logical processor specific (TI).

Some of the Pentium 4 and Intel Xeon processor performance-monitoring events may be available only to specific

models. The performance-monitoring events listed in Tables 19-28 and 19-29 apply to processors with CPUID

signature that matches family encoding 15, model encoding 0, 1, 2 3, 4, or 6. Table applies to processors with a

CPUID signature that matches family encoding 15, model encoding 3, 4 or 6.

The functionality of performance-monitoring events in Pentium 4 and Intel Xeon processors is also available when

IA-32e mode is enabled.

D9H

SIMD_FP_DP_P_

Comp_Ret

02H

Number of SSE/SSE2 packed double precision

compute instructions retired (does not include AND,

OR, XOR).

D9H

SIMD_FP_DP_S_

Comp_Ret

03H

Number of SSE/SSE2 scalar double precision

compute instructions retired (does not include AND,

OR, XOR).

DAH

Fused_Uops_Ret

00H

All fused uops retired.

DAH

Fused_Ld_Uops_

Ret

01H

Fused load uops retired.

DAH

Fused_St_Uops_Ret 02H

Fused store uops retired.

DBH

Unfusion

00H

Number of unfusion events in the ROB (due to

exception).

E0H

Br_Instr_Decoded

00H

Branch instructions decoded.

E2H

BTB_Misses

00H

Number of branches the BTB did not produce a

prediction.

E4H

Br_Bogus

00H

Number of bogus branches.

E6H

BAClears

00H

Number of BAClears asserted.

F0H

Pref_Rqsts_Up

00H

Number of hardware prefetch requests issued in

forward streams.

F8H

Pref_Rqsts_Dn

00H

Number of hardware prefetch requests issued in

backward streams.

Table 19-28. Performance Monitoring Events Supported by Intel NetBurst® Microarchitecture

for Non-Retirement Counting

Event Name

Event Parameters Parameter Value

Description

TC_deliver_mode

This event counts the duration (in clock cycles) of the operating

modes of the trace cache and decode engine in the processor

package. The mode is specified by one or more of the event mask

bits.

Table 19-27. Non-Architectural Performance Events in Intel® Core™ Solo and Intel® Core™ Duo Processors (Contd.)

Event

Num.

Event Mask

Mnemonic

Umask

Value

Description

Comment