18-16 Vol. 3B

PERFORMANCE MONITORING

Some performance events may (a) support none of the three event-specific qualification encodings (b) may

support core-specificity and agent specificity simultaneously (c) or may support core-specificity and hardware

prefetch qualification simultaneously. Agent-specificity and hardware prefetch qualification are mutually exclusive.

In addition, some L2 events permit qualifications that distinguish cache coherent states. The sub-field definition for

cache coherency state qualification is shown in Table 18-5. If no bits in the MESI qualification sub-field are set for

an event that requires setting MESI qualification bits, the event count will not increment.

18.4

PERFORMANCE MONITORING (PROCESSORS BASED ON INTEL

®

CORE

™

MICROARCHITECTURE)

In addition to architectural performance monitoring, processors based on the Intel Core microarchitecture support

non-architectural performance monitoring events.

Architectural performance events can be collected using general-purpose performance counters. Non-architectural

performance events can be collected using general-purpose performance counters (coupled with two

IA32_PERFEVTSELx MSRs for detailed event configurations), or fixed-function performance counters (see Section

18.4.1). IA32_PERFEVTSELx MSRs are architectural; their layout is shown in Figure 18-1. Starting with Intel Core

2 processor T 7700, fixed-function performance counters and associated counter control and status MSR becomes

part of architectural performance monitoring version 2 facilities (see also Section 18.2.2).

Non-architectural performance events in processors based on Intel Core microarchitecture use event select values

that are model-specific. Valid event mask (Umask) bits are listed in Chapter 19. The UMASK field may contain sub-

fields identical to those listed in Table 18-2, Table 18-3, Table 18-4, and Table 18-5. One or more of these sub-

fields may apply to specific events on an event-by-event basis. Details are listed in Table 19-23 in Chapter 19,

“Performance-Monitoring Events.”

In addition, the UMASK filed may also contain a sub-field that allows detection specificity related to snoop

responses. Bits of the snoop response qualification sub-field are defined in Table 18-6.

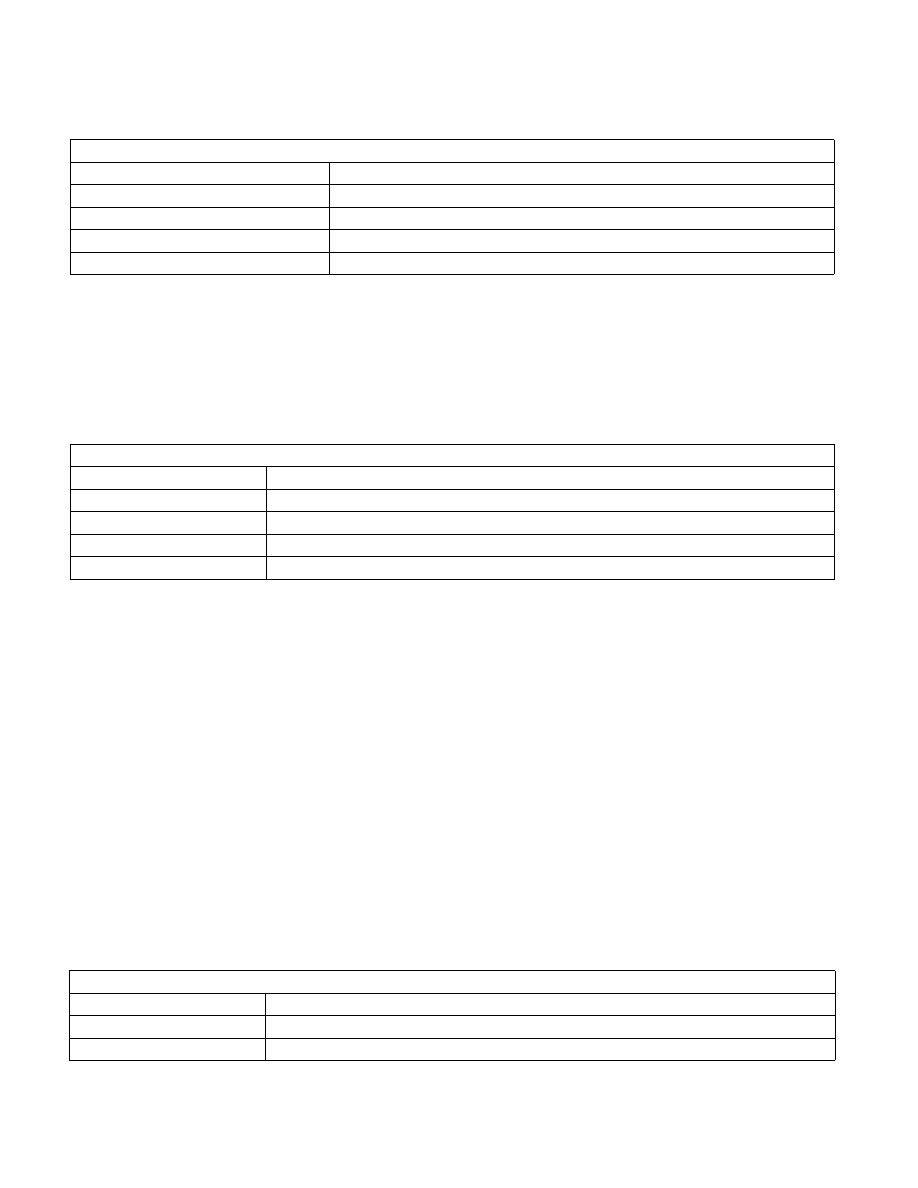

Table 18-4. HW Prefetch Qualification Encoding within a Non-Architectural Umask

IA32_PERFEVTSELx MSRs

Bit 13:12 Encoding

Description

11B

All inclusive

10B

Reserved

01B

Hardware prefetch only

00B

Exclude hardware prefetch

Table 18-5. MESI Qualification Definitions within a Non-Architectural Umask

IA32_PERFEVTSELx MSRs

Bit Position 11:8

Description

Bit 11

Counts modified state

Bit 10

Counts exclusive state

Bit 9

Counts shared state

Bit 8

Counts Invalid state

Table 18-6. Bus Snoop Qualification Definitions within a Non-Architectural Umask

IA32_PERFEVTSELx MSRs

Bit Position 11:8

Description

Bit 11

HITM response

Bit 10

Reserved