Vol. 3B 18-3

PERFORMANCE MONITORING

•

Number of performance monitoring counters available in a logical processor (each IA32_PERFEVTSELx MSR is

paired to the corresponding IA32_PMCx MSR)

•

Number of bits supported in each IA32_PMCx

•

Number of architectural performance monitoring events supported in a logical processor

Software can use CPUID to discover architectural performance monitoring availability (CPUID.0AH). The architec-

tural performance monitoring leaf provides an identifier corresponding to the version number of architectural

performance monitoring available in the processor.

The version identifier is retrieved by querying CPUID.0AH:EAX[bits 7:0] (see Chapter 3, “Instruction Set Refer-

ence, A-L,” in the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 2A). If the version iden-

tifier is greater than zero, architectural performance monitoring capability is supported. Software queries the

CPUID.0AH for the version identifier first; it then analyzes the value returned in CPUID.0AH.EAX, CPUID.0AH.EBX

to determine the facilities available.

In the initial implementation of architectural performance monitoring; software can determine how many

IA32_PERFEVTSELx/ IA32_PMCx MSR pairs are supported per core, the bit-width of PMC, and the number of archi-

tectural performance monitoring events available.

18.2.1.1 Architectural Performance Monitoring Version 1 Facilities

Architectural performance monitoring facilities include a set of performance monitoring counters and performance

event select registers. These MSRs have the following properties:

•

IA32_PMCx MSRs start at address 0C1H and occupy a contiguous block of MSR address space; the number of

MSRs per logical processor is reported using CPUID.0AH:EAX[15:8].

•

IA32_PERFEVTSELx MSRs start at address 186H and occupy a contiguous block of MSR address space. Each

performance event select register is paired with a corresponding performance counter in the 0C1H address

block.

•

The bit width of an IA32_PMCx MSR is reported using the CPUID.0AH:EAX[23:16]. This the number of valid bits

for read operation. On write operations, the lower-order 32 bits of the MSR may be written with any value, and

the high-order bits are sign-extended from the value of bit 31.

•

Bit field layout of IA32_PERFEVTSELx MSRs is defined architecturally.

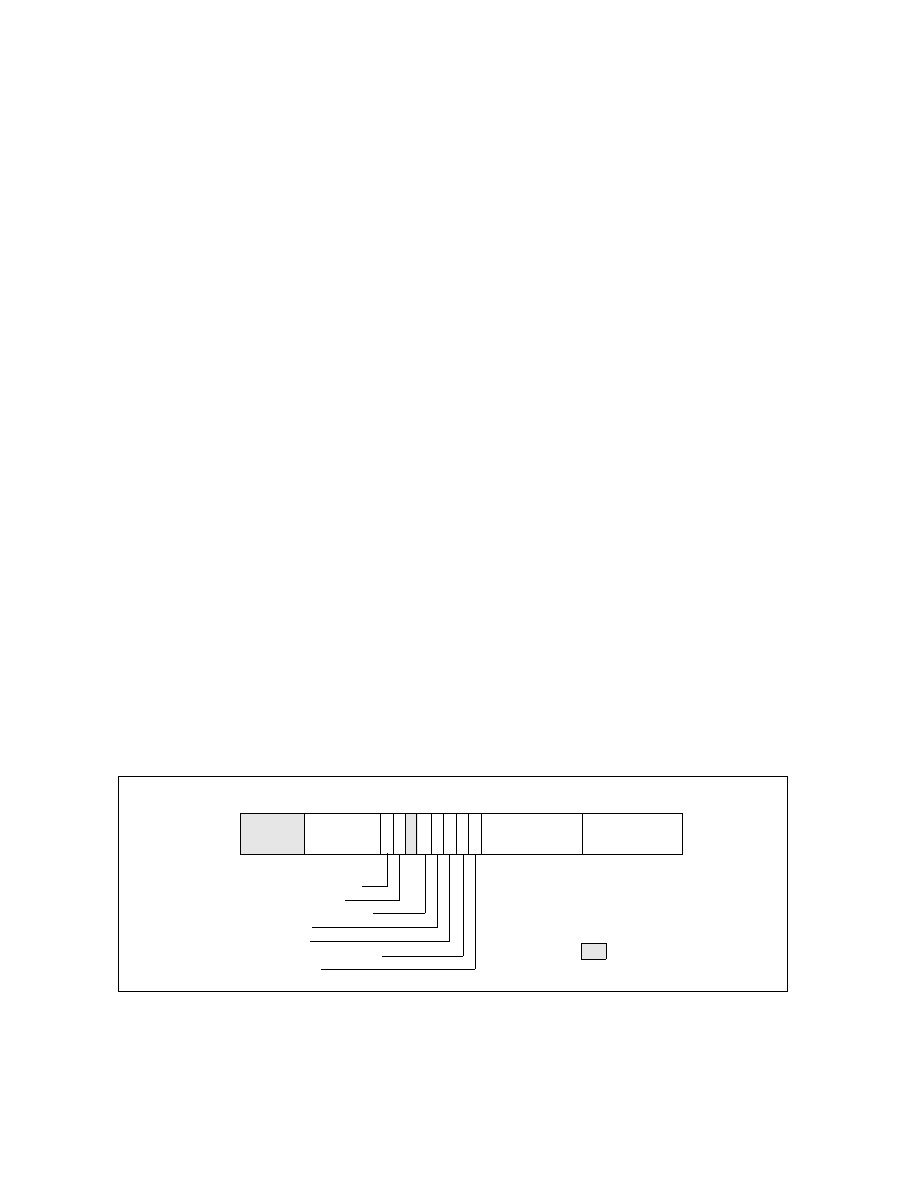

See Figure 18-1 for the bit field layout of IA32_PERFEVTSELx MSRs. The bit fields are:

•

Event select field (bits 0 through 7) — Selects the event logic unit used to detect microarchitectural

conditions (see Table 18-1, for a list of architectural events and their 8-bit codes). The set of values for this field

is defined architecturally; each value corresponds to an event logic unit for use with an architectural

performance event. The number of architectural events is queried using CPUID.0AH:EAX. A processor may

support only a subset of pre-defined values.

Figure 18-1. Layout of IA32_PERFEVTSELx MSRs

31

INV—Invert counter mask

EN—Enable counters

INT—APIC interrupt enable

PC—Pin control

8 7

0

Event Select

E—Edge detect

OS—Operating system mode

USR—User Mode

Counter Mask

E

E

N

I

N

T

19

16

18

15

17

20

21

22

23

24

Reserved

I

N

V

P

C

U

S

R

O

S

Unit Mask (UMASK)

(CMASK)

63