Vol. 3B 18-15

PERFORMANCE MONITORING

If IA32_A_PMCi is present, the 64-bit input value (EDX:EAX) of WRMSR to IA32_A_PMCi will cause IA32_PMCi to

be updated by:

COUNTERWIDTH = CPUID.0AH:EAX[23:16] bit width of the performance monitoring counter

IA32_PMCi[COUNTERWIDTH-1:32] ‚Üê EDX[COUNTERWIDTH-33:0]);

IA32_PMCi[31:0] ‚Üê EAX[31:0];

EDX[63:COUNTERWIDTH] are reserved

18.3

PERFORMANCE MONITORING (INTEL® CORE™ SOLO AND INTEL® CORE™ DUO

PROCESSORS)

In Intel Core Solo and Intel Core Duo processors, non-architectural performance monitoring events are

programmed using the same facilities (see Figure 18-1) used for architectural performance events.

Non-architectural performance events use event select values that are model-specific. Event mask (Umask) values

are also specific to event logic units. Some microarchitectural conditions detectable by a Umask value may have

specificity related to processor topology (see Section 8.6, “Detecting Hardware Multi-Threading Support and

Topology,” in the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3A). As a result, the unit

mask field (for example, IA32_PERFEVTSELx[bits 15:8]) may contain sub-fields that specify topology information

of processor cores.

The sub-field layout within the Umask field may support two-bit encoding that qualifies the relationship between a

microarchitectural condition and the originating core. This data is shown in Table 18-2. The two-bit encoding for

core-specificity is only supported for a subset of Umask values (see Chapter 19, “Performance Monitoring Events”)

and for Intel Core Duo processors. Such events are referred to as core-specific events.

Some microarchitectural conditions allow detection specificity only at the boundary of physical processors. Some

bus events belong to this category, providing specificity between the originating physical processor (a bus agent)

versus other agents on the bus. Sub-field encoding for agent specificity is shown in Table 18-3.

Some microarchitectural conditions are detectable only from the originating core. In such cases, unit mask does

not support core-specificity or agent-specificity encodings. These are referred to as core-only conditions.

Some microarchitectural conditions allow detection specificity that includes or excludes the action of hardware

prefetches. A two-bit encoding may be supported to qualify hardware prefetch actions. Typically, this applies only

to some L2 or bus events. The sub-field encoding for hardware prefetch qualification is shown in Table 18-4.

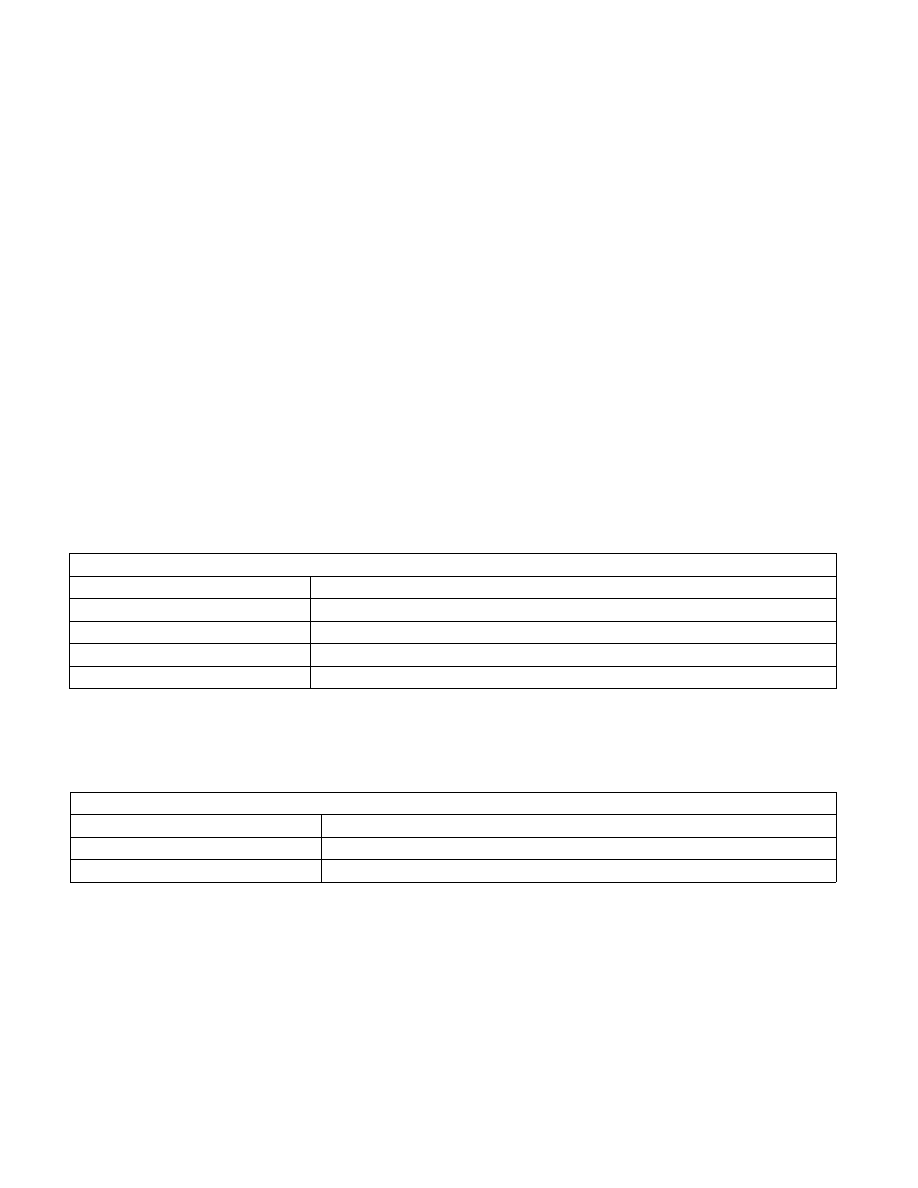

Table 18-2. Core Specificity Encoding within a Non-Architectural Umask

IA32_PERFEVTSELx MSRs

Bit 15:14 Encoding

Description

11B

All cores

10B

Reserved

01B

This core

00B

Reserved

Table 18-3. Agent Specificity Encoding within a Non-Architectural Umask

IA32_PERFEVTSELx MSRs

Bit 13 Encoding

Description

0

This agent

1

Include all agents