Vol. 3B 18-17

PERFORMANCE MONITORING

There are also non-architectural events that support qualification of different types of snoop operation. The corre-

sponding bit field for snoop type qualification are listed in Table 18-7.

No more than one sub-field of MESI, snoop response, and snoop type qualification sub-fields can be supported in a

performance event.

NOTE

Software must write known values to the performance counters prior to enabling the counters. The

content of general-purpose counters and fixed-function counters are undefined after INIT or

RESET.

18.4.1

Fixed-function Performance Counters

Processors based on Intel Core microarchitecture provide three fixed-function performance counters. Bits beyond

the width of the fixed counter are reserved and must be written as zeros. Model-specific fixed-function perfor-

mance counters on processors that support Architectural Perfmon version 1 are 40 bits wide.

Each of the fixed-function counter is dedicated to count a pre-defined performance monitoring events. The perfor-

mance monitoring events associated with fixed-function counters and the addresses of these counters are listed in

Table 18-8.

Programming the fixed-function performance counters does not involve any of the IA32_PERFEVTSELx MSRs, and

does not require specifying any event masks. Instead, the MSR MSR_PERF_FIXED_CTR_CTRL provides multiple

sets of 4-bit fields; each 4-bit field controls the operation of a fixed-function performance counter (PMC). See

Figures 18-14. Two sub-fields are defined for each control. See Figure 18-14; bit fields are:

•

Enable field (low 2 bits in each 4-bit control) — When bit 0 is set, performance counting is enabled in the

corresponding fixed-function performance counter to increment when the target condition associated with the

architecture performance event occurs at ring 0.

When bit 1 is set, performance counting is enabled in the corresponding fixed-function performance counter to

increment when the target condition associated with the architecture performance event occurs at ring greater

than 0.

Bit 9

HIT response

Bit 8

CLEAN response

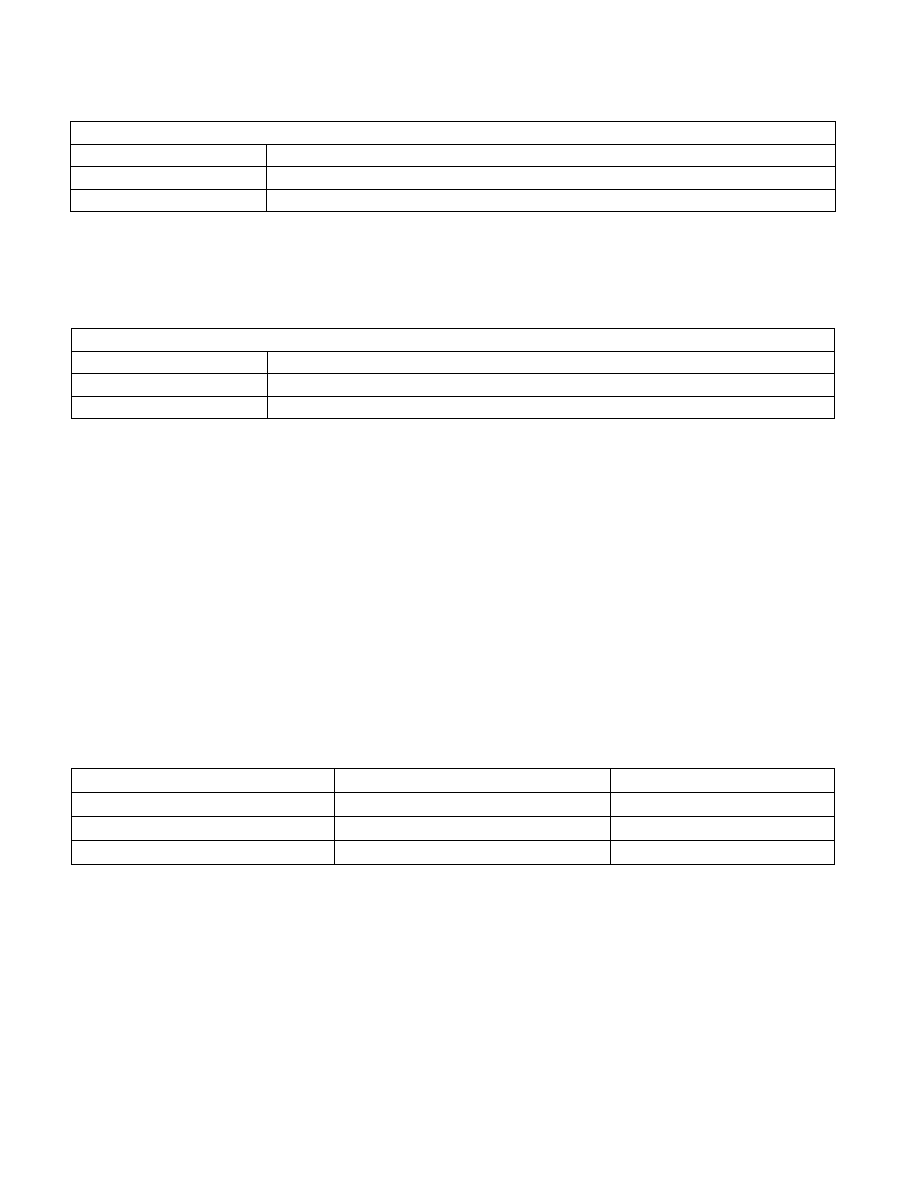

Table 18-7. Snoop Type Qualification Definitions within a Non-Architectural Umask

IA32_PERFEVTSELx MSRs

Bit Position 9:8

Description

Bit 9

CMP2I snoops

Bit 8

CMP2S snoops

Table 18-8. Association of Fixed-Function Performance Counters with Architectural Performance Events

Event Name

Fixed-Function PMC

PMC Address

INST_RETIRED.ANY

MSR_PERF_FIXED_CTR0/IA32_FIXED_CTR0

309H

CPU_CLK_UNHALTED.CORE

MSR_PERF_FIXED_CTR1//IA32_FIXED_CTR1

30AH

CPU_CLK_UNHALTED.REF

MSR_PERF_FIXED_CTR2//IA32_FIXED_CTR2

30BH

Table 18-6. Bus Snoop Qualification Definitions within a Non-Architectural Umask

IA32_PERFEVTSELx MSRs

Bit Position 11:8

Description