19-118 Vol. 3B

PERFORMANCE-MONITORING EVENTS

Table 19-23 lists general-purpose non-architectural performance-monitoring events supported in processors based

on Intel

®

Core™ microarchitecture. For convenience, Table 19-23 also includes architectural events and describes

minor model-specific behavior where applicable. Software must use a general-purpose performance counter to

count events listed in Table 19-23.

This event is not affected by core frequency changes

(e.g., P states) but counts at the same frequency as

the time stamp counter. This event can approximate

elapsed time while the core was not in halt state and

not in a TM stop-clock state.

This event has a constant ratio with the

CPU_CLK_UNHALTED.BUS event.

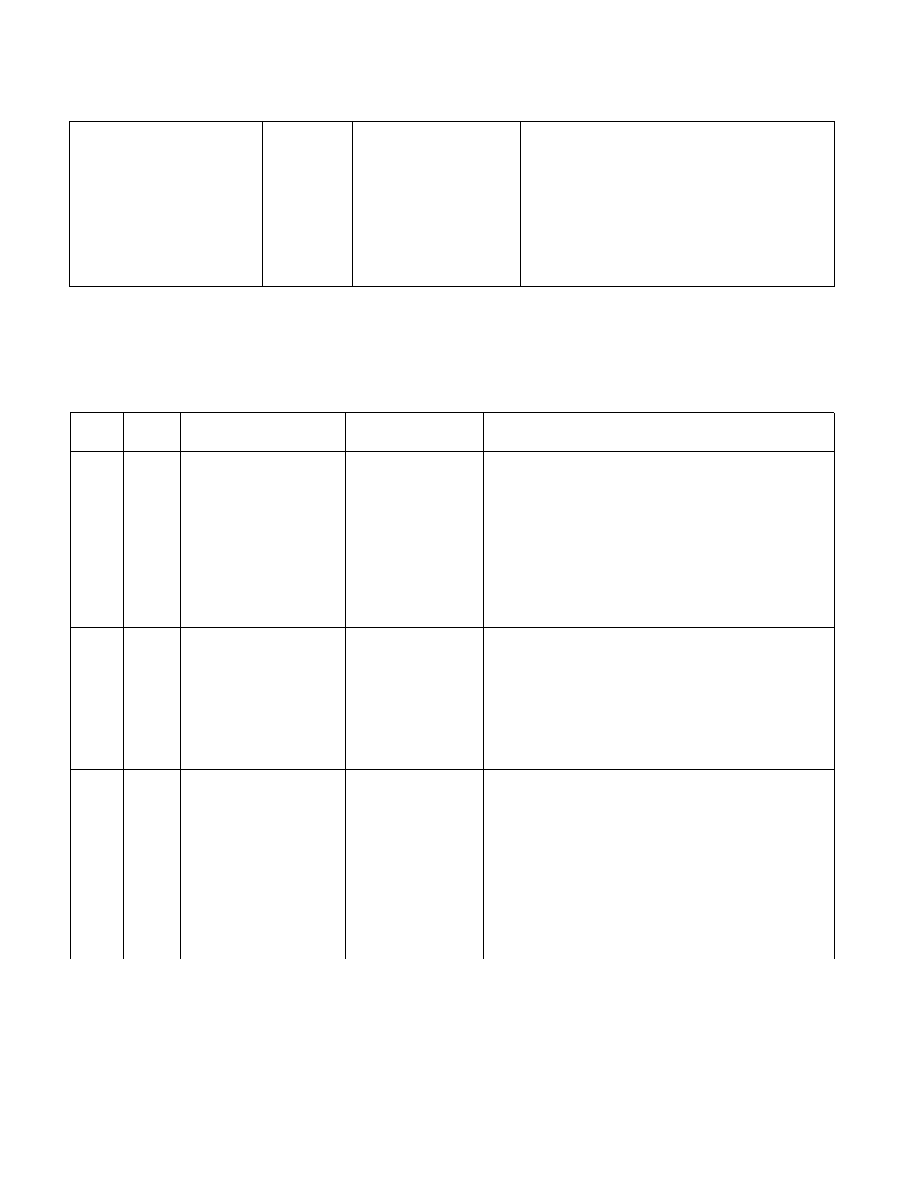

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment

03H

02H

LOAD_BLOCK.STA

Loads blocked by a

preceding store with

unknown address.

This event indicates that loads are blocked by preceding

stores. A load is blocked when there is a preceding store to

an address that is not yet calculated. The number of events

is greater or equal to the number of load operations that

were blocked.

If the load and the store are always to different addresses,

check why the memory disambiguation mechanism is not

working. To avoid such blocks, increase the distance

between the store and the following load so that the store

address is known at the time the load is dispatched.

03H

04H

LOAD_BLOCK.STD

Loads blocked by a

preceding store with

unknown data.

This event indicates that loads are blocked by preceding

stores. A load is blocked when there is a preceding store to

the same address and the stored data value is not yet

known. The number of events is greater or equal to the

number of load operations that were blocked.

To avoid such blocks, increase the distance between the

store and the dependent load, so that the store data is

known at the time the load is dispatched.

03H

08H

LOAD_BLOCK.

OVERLAP_STORE

Loads that partially

overlap an earlier

store, or 4-Kbyte

aliased with a previous

store.

This event indicates that loads are blocked due to a variety

of reasons. Some of the triggers for this event are when a

load is blocked by a preceding store, in one of the following:

• Some of the loaded byte locations are written by the

preceding store and some are not.

• The load is from bytes written by the preceding store,

the store is aligned to its size and either:

• The load’s data size is one or two bytes and it is not

aligned to the store.

• The load’s data size is of four or eight bytes and the load

is misaligned.

Table 19-22. Fixed-Function Performance Counter and Pre-defined Performance Events (Contd.)

Fixed-Function Performance

Counter

Address

Event Mask Mnemonic

Description