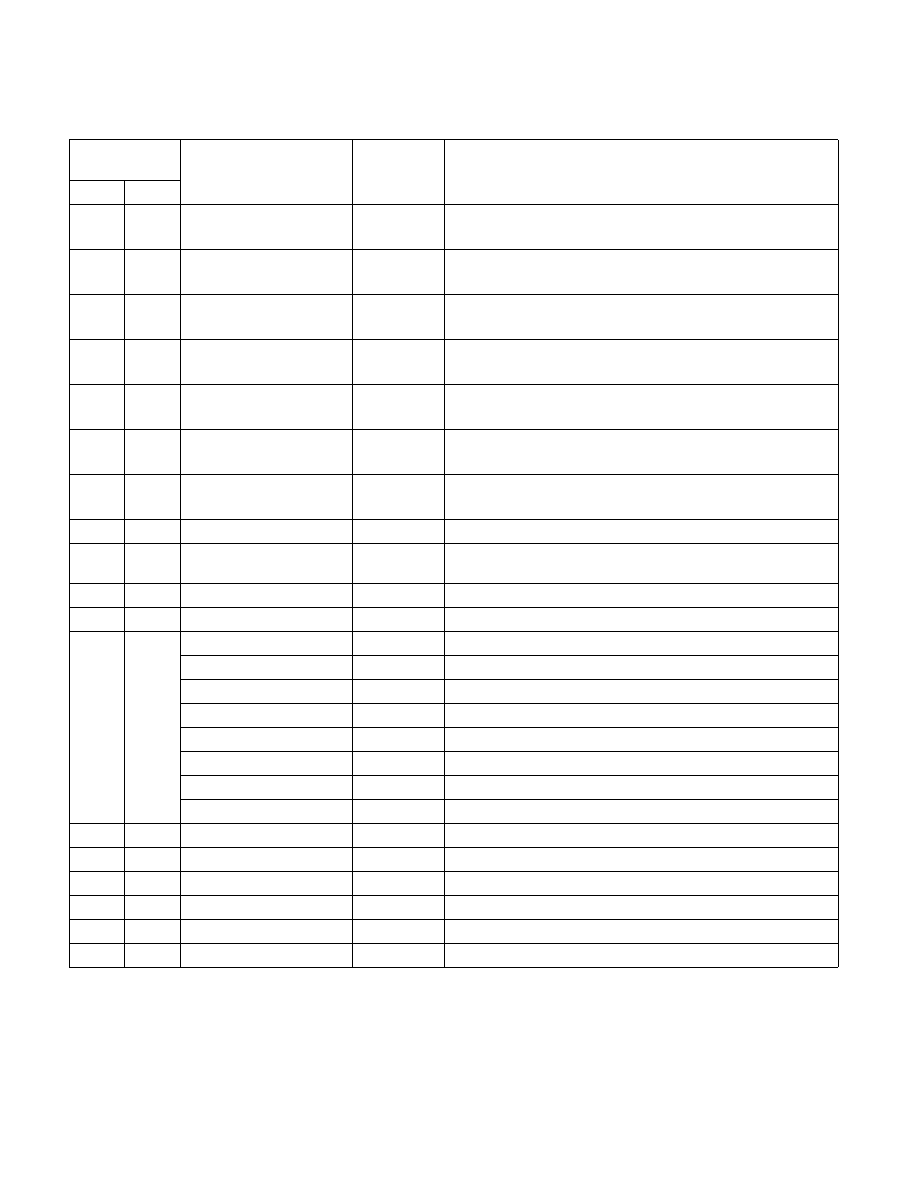

Vol. 3C 35-257

MODEL-SPECIFIC REGISTERS (MSRS)

6D9H

1753

MSR_

LASTBRANCH_25_TO_IP

Thread

Last Branch Record 25 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6DAH

1754

MSR_

LASTBRANCH_26_TO_IP

Thread

Last Branch Record 26 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6DBH

1755

MSR_

LASTBRANCH_27_TO_IP

Thread

Last Branch Record 27 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6DCH

1756

MSR_

LASTBRANCH_28_TO_IP

Thread

Last Branch Record 28 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6DDH

1757

MSR_

LASTBRANCH_29_TO_IP

Thread

Last Branch Record 29 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6DEH

1758

MSR_

LASTBRANCH_30_TO_IP

Thread

Last Branch Record 30 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

6DFH

1759

MSR_

LASTBRANCH_31_TO_IP

Thread

Last Branch Record 31 To IP (R/W)

See description of MSR_LASTBRANCH_0_TO_IP.

770H

1904

IA32_PM_ENABLE

Package

See Section 14.4.2, “Enabling HWP”

771H

1905

IA32_HWP_CAPABILITIES

Thread

See Section 14.4.3, “HWP Performance Range and Dynamic

772H

1906

IA32_HWP_REQUEST_PKG

Package

See Section 14.4.4, “Managing HWP”

773H

1907

IA32_HWP_INTERRUPT

Thread

See Section 14.4.6, “HWP Notifications”

774H

1908

IA32_HWP_REQUEST

Thread

See Section 14.4.4, “Managing HWP”

7:0

Minimum Performance (R/W).

15:8

Maximum Performance (R/W).

23:16

Desired Performance (R/W).

31:24

Energy/Performance Preference (R/W).

41:32

Activity Window (R/W).

42

Package Control (R/W).

63:43

Reserved.

777H

1911

IA32_HWP_STATUS

Thread

See Section 14.4.5, “HWP Feedback”

D90H

3472

IA32_BNDCFGS

Thread

See Table 35-2.

DA0H

3488

IA32_XSS

Thread

See Table 35-2.

DB0H

3504

IA32_PKG_HDC_CTL

Package

See Section 14.5.2, “Package level Enabling HDC”

DB1H

3505

IA32_PM_CTL1

Thread

See Section 14.5.3, “Logical-Processor Level HDC Control”

DB2H

3506

IA32_THREAD_STALL

Thread

See Section 14.5.4.1, “IA32_THREAD_STALL”

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec