Vol. 3B 14-7

POWER AND THERMAL MANAGEMENT

14.4.2 Enabling

HWP

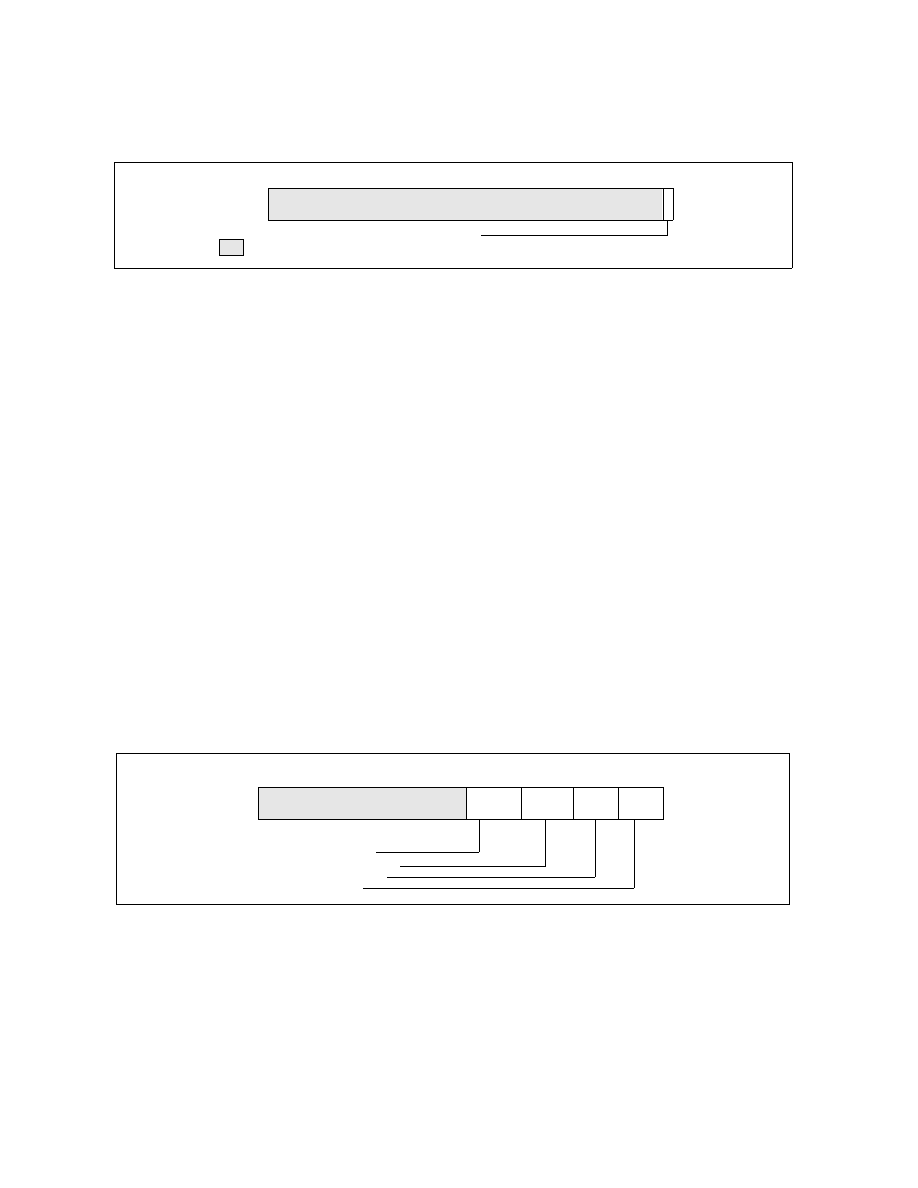

The layout of the IA32_PM_ENABLE MSR is shown in Figure 14-4. The bit fields are described below:

•

HWP_ENABLE (bit 0, R/W1Once) — Software sets this bit to enable HWP with autonomous selection. When

set, the processor will disregard input from the legacy performance control interface (IA32_PERF_CTL). Note

this bit can only be enabled once from the default value. Once set, writes to the HWP_ENABLE bit are ignored.

Only RESET will clear this bit. Default = zero (0).

•

Bits 63:1 are reserved and must be zero.

After software queries CPUID and verifies the processor’s support of HWP, system software can write 1 to

IA32_PM_ENABLE.HWP_ENABLE (bit 0) to enable hardware controlled performance states. The default value of

IA32_PM_ENABLE MSR at power-on is 0, i.e. HWP is disabled.

Additional MSRs associated with HWP may only be accessed after HWP is enabled, with the exception of

IA32_HWP_INTERRUPT and MSR_PPERF. Accessing the IA32_HWP_INTERRUPT MSR requires only HWP is present

as enumerated by CPUID but does not require enabling HWP.

IA32_PM_ENABLE is a package level MSR, i.e. writing to it from any logical processor within a package affects all

logical processors within that package.

14.4.3

HWP Performance Range and Dynamic Capabilities

The OS reads the IA32_HWP_CAPABILITIES MSR to comprehend the limits of the HWP-managed performance

range as well as the dynamic capability, which may change during processor operation. The enumerated perfor-

mance range values reported by IA32_HWP_CAPABILITIES directly map to initial frequency targets (prior to work-

load-specific frequency optimizations of HWP). However the mapping is processor family specific.

The layout of the IA32_HWP_CAPABILITIES MSR is shown in Figure 14-5. The bit fields are described below:

•

Highest_Performance (bits 7:0, RO) — Value for the maximum non-guaranteed performance level.

•

Guaranteed_Performance (bits 15:8, RO) — Current value for the guaranteed performance level. This

value can change dynamically as a result of internal or external constraints, e.g. thermal or power limits.

•

Most_Efficient_Performance (bits 23:16, RO) — Current value of the most efficient performance level.

This value can change dynamically as a result of workload characteristics.

Figure 14-4. IA32_PM_ENABLE MSR

Figure 14-5. IA32_HWP_CAPABILITIES Register

63

0

Reserved

1

HWP_ENABLE

Reserved

63

0

Reserved

24

7

8

15

16

23

31

32

Most_Efficient_Performance

Guaranteed_Performance

Highest_Performance

Lowest_Performance