35-204 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.11.2 Additional Residency MSRs Supported in 4th Generation Intel® Core™

Processors

The 4th generation Intel

®

Core™ processor family (based on Haswell microarchitecture) with CPUID

DisplayFamily_DisplayModel signature 06_45H supports the MSR interfaces listed in Table 35-18, Table 35-19,

Table 35-27, Table 35-28, and Table 35-29.

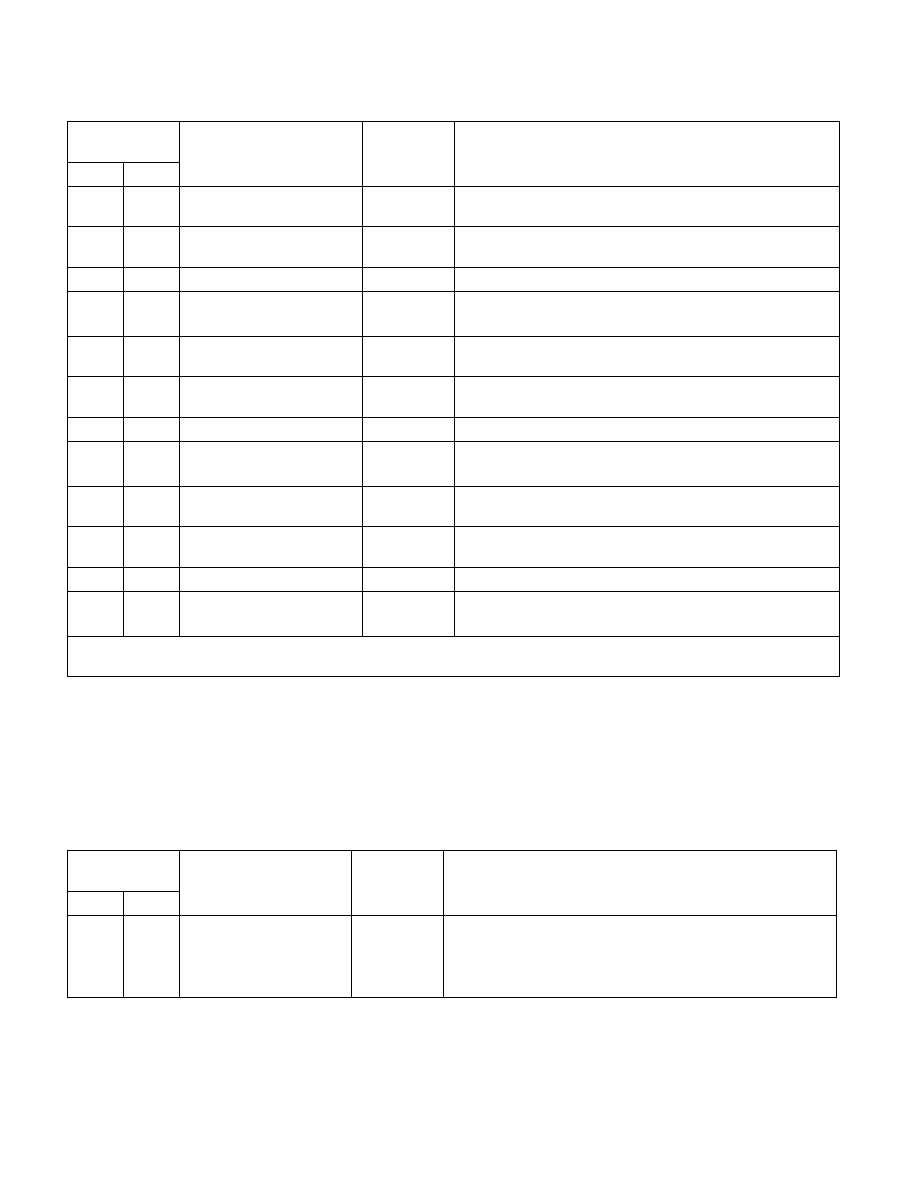

710H

1808

MSR_UNC_CBO_1_

PERFEVTSEL0

Package

Uncore C-Box 1, counter 0 event select MSR

711H

1809

MSR_UNC_CBO_1_

PERFEVTSEL1

Package

Uncore C-Box 1, counter 1 event select MSR

716H

1814

MSR_UNC_CBO_1_PERFCTR0 Package

Uncore C-Box 1, performance counter 0

717H

1815

MSR_UNC_CBO_1_PERFCTR1 Package

Uncore C-Box 1, performance counter 1

720H

1824

MSR_UNC_CBO_2_

PERFEVTSEL0

Package

Uncore C-Box 2, counter 0 event select MSR

721H

1824

MSR_UNC_CBO_2_

PERFEVTSEL1

Package

Uncore C-Box 2, counter 1 event select MSR

726H

1830

MSR_UNC_CBO_2_PERFCTR0 Package

Uncore C-Box 2, performance counter 0

727H

1831

MSR_UNC_CBO_2_PERFCTR1 Package

Uncore C-Box 2, performance counter 1

730H

1840

MSR_UNC_CBO_3_

PERFEVTSEL0

Package

Uncore C-Box 3, counter 0 event select MSR

731H

1841

MSR_UNC_CBO_3_

PERFEVTSEL1

Package

Uncore C-Box 3, counter 1 event select MSR.

736H

1846

MSR_UNC_CBO_3_PERFCTR0 Package

Uncore C-Box 3, performance counter 0.

737H

1847

MSR_UNC_CBO_3_PERFCTR1 Package

Uncore C-Box 3, performance counter 1.

See Table 35-18, Table 35-19, Table 35-20, Table 35-23, Table 35-27 for other MSR definitions applicable to processors with CPUID

signatures 063CH, 06_46H.

Table 35-29. Additional Residency MSRs Supported by 4th Generation Intel® Core™ Processors with

DisplayFamily_DisplayModel Signature 06_45H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Core

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-states.

See http://biosbits.org.

Table 35-28. MSRs Supported by 4th Generation Intel® Core™ Processors (Haswell microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec