27-14 Vol. 3C

VM EXITS

•

VM-exit instruction information. For VM exits due to attempts to execute INS, INVEPT, INVPCID, INVVPID,

LIDT, LGDT, LLDT, LTR, OUTS, RDRAND, RDSEED, SIDT, SGDT, SLDT, STR, VMCLEAR, VMPTRLD, VMPTRST,

VMREAD, VMWRITE, VMXON, XRSTORS, or XSAVES, this field receives information about the instruction that

caused the VM exit. The format of the field depends on the identity of the instruction causing the VM exit:

— For VM exits due to attempts to execute INS or OUTS, the field has the format is given in Table 27-8.

1

— For VM exits due to attempts to execute INVEPT, INVPCID, or INVVPID, the field has the format is given in

— For VM exits due to attempts to execute LIDT, LGDT, SIDT, or SGDT, the field has the format is given in

— For VM exits due to attempts to execute LLDT, LTR, SLDT, or STR, the field has the format is given in

— For VM exits due to attempts to execute RDRAND or RDSEED, the field has the format is given in

— For VM exits due to attempts to execute VMCLEAR, VMPTRLD, VMPTRST, VMXON, XRSTORS, or XSAVES,

the field has the format is given in Table 27-13.

— For VM exits due to attempts to execute VMREAD or VMWRITE, the field has the format is given in

For all other VM exits, the field is undefined, unless the VM exit occurred in enclave mode, in which case the

field is cleared.

•

I/O RCX, I/O RSI, I/O RDI, I/O RIP. These fields are undefined except for SMM VM exits due to system-

management interrupts (SMIs) that arrive immediately after retirement of I/O instructions. See Section

34.15.2.3. Note that, if the VM exit occurred in enclave mode, these fields are all cleared.

17:15

Segment register:

0: ES

1: CS

2: SS

3: DS

4: FS

5: GS

Other values not used. Undefined for VM exits due to execution of INS.

31:18

Undefined.

1. The format of the field was undefined for these VM exits on the first processors to support the virtual-machine extensions. Soft-

ware can determine whether the format specified in Table 27-8 is used by consulting the VMX capability MSR IA32_VMX_BASIC

(see Appendix A.1).

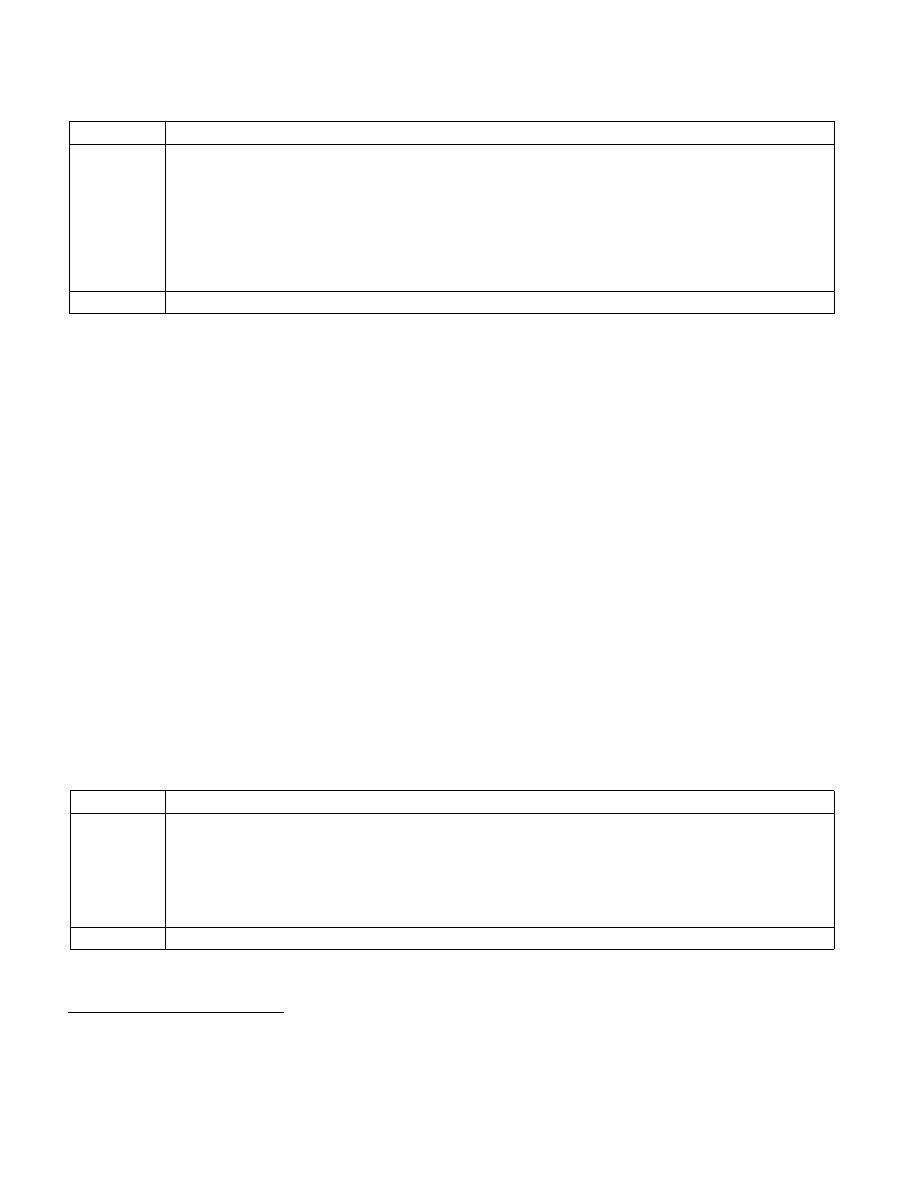

Table 27-9. Format of the VM-Exit Instruction-Information Field as Used for INVEPT, INVPCID, and INVVPID

Bit Position(s) Content

1:0

Scaling:

0: no scaling

1: scale by 2

2: scale by 4

3: scale by 8 (used only on processors that support Intel 64 architecture)

Undefined for instructions with no index register (bit 22 is set).

6:2

Undefined.

Table 27-8. Format of the VM-Exit Instruction-Information Field as Used for INS and OUTS (Contd.)

Bit Position(s) Content