Vol. 3C 27-15

VM EXITS

9:7

Address size:

0: 16-bit

1: 32-bit

2: 64-bit (used only on processors that support Intel 64 architecture)

Other values not used.

10

Cleared to 0.

14:11

Undefined.

17:15

Segment register:

0: ES

1: CS

2: SS

3: DS

4: FS

5: GS

Other values not used.

21:18

IndexReg:

0 = RAX

1 = RCX

2 = RDX

3 = RBX

4 = RSP

5 = RBP

6 = RSI

7 = RDI

8–15 represent R8–R15, respectively (used only on processors that support Intel 64 architecture)

Undefined for instructions with no index register (bit 22 is set).

22

IndexReg invalid (0 = valid; 1 = invalid)

26:23

BaseReg (encoded as IndexReg above)

Undefined for memory instructions with no base register (bit 27 is set).

27

BaseReg invalid (0 = valid; 1 = invalid)

31:28

Reg2 (same encoding as IndexReg above)

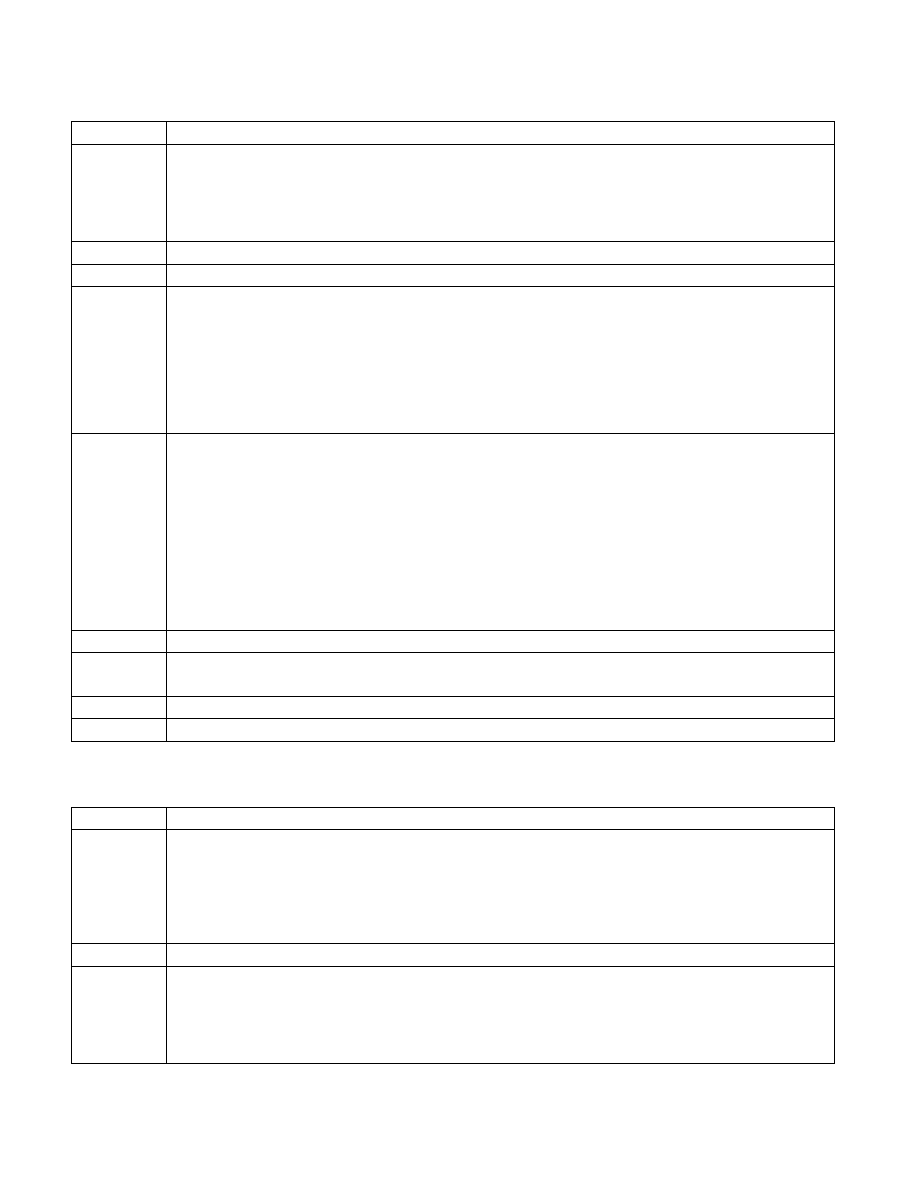

Table 27-10. Format of the VM-Exit Instruction-Information Field as Used for LIDT, LGDT, SIDT, or SGDT

Bit Position(s) Content

1:0

Scaling:

0: no scaling

1: scale by 2

2: scale by 4

3: scale by 8 (used only on processors that support Intel 64 architecture)

Undefined for instructions with no index register (bit 22 is set).

6:2

Undefined.

9:7

Address size:

0: 16-bit

1: 32-bit

2: 64-bit (used only on processors that support Intel 64 architecture)

Other values not used.

Table 27-9. Format of the VM-Exit Instruction-Information Field as Used for INVEPT, INVPCID, and INVVPID (Contd.)

Bit Position(s) Content