Vol. 3C 27-19

VM EXITS

21:18

IndexReg:

0 = RAX

1 = RCX

2 = RDX

3 = RBX

4 = RSP

5 = RBP

6 = RSI

7 = RDI

8–15 represent R8–R15, respectively (used only on processors that support Intel 64 architecture)

Undefined for instructions with no index register (bit 22 is set).

22

IndexReg invalid (0 = valid; 1 = invalid)

26:23

BaseReg (encoded as IndexReg above)

Undefined for instructions with no base register (bit 27 is set).

27

BaseReg invalid (0 = valid; 1 = invalid)

31:28

Undefined.

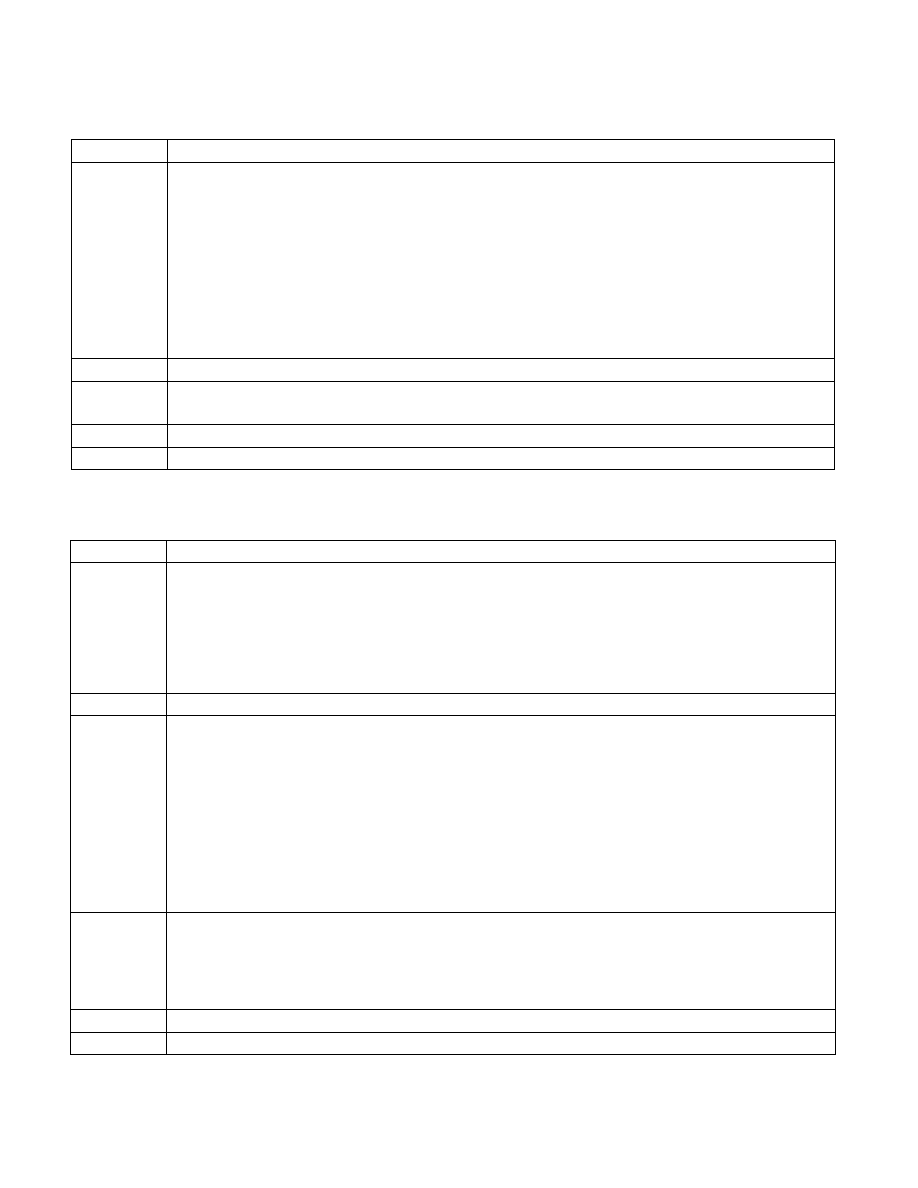

Table 27-14. Format of the VM-Exit Instruction-Information Field as Used for VMREAD and VMWRITE

Bit Position(s) Content

1:0

Scaling:

0: no scaling

1: scale by 2

2: scale by 4

3: scale by 8 (used only on processors that support Intel 64 architecture)

Undefined for register instructions (bit 10 is set) and for memory instructions with no index register (bit 10 is clear

and bit 22 is set).

2

Undefined.

6:3

Reg1:

0 = RAX

1 = RCX

2 = RDX

3 = RBX

4 = RSP

5 = RBP

6 = RSI

7 = RDI

8–15 represent R8–R15, respectively (used only on processors that support Intel 64 architecture)

Undefined for memory instructions (bit 10 is clear).

9:7

Address size:

0: 16-bit

1: 32-bit

2: 64-bit (used only on processors that support Intel 64 architecture)

Other values not used. Undefined for register instructions (bit 10 is set).

10

Mem/Reg (0 = memory; 1 = register).

14:11

Undefined.

Table 27-13. Format of the VM-Exit Instruction-Information Field as Used for VMCLEAR, VMPTRLD, VMPTRST,

VMXON, XRSTORS, and XSAVES (Contd.)

Bit Position(s) Content