18-76 Vol. 3B

PERFORMANCE MONITORING

The layout of PEBS records are largely identical to those shown in Table 18-44.

The PEBS records at offsets 98H, A0H, and ABH record data gathered from three of the PEBS capabilities in prior

processor generations: load latency facility (Section 18.9.4.2), PDIR (Section 18.9.4.4), and data address profiling

(Section 18.11.3).

In the core PMU of the 6th generation processor, load latency facility and PDIR capabilities and data address

profiling are unchanged relative to the 4th and 5th generation Intel Core processors. Similarly, precise store is

replaced by data address profiling.

With format 0010b, a snapshot of the IA32_PERF_GLOBAL_STATUS may be useful to resolve the situations when

more than one of IA32_PMICx have been configured to collect PEBS data and two consecutive overflows of the

PEBS-enabled counters are sufficiently far apart in time. It is also possible for the image at 90H to indicate multiple

PEBS-enabled counters have overflowed. In the latter scenario, software cannot to correlate the PEBS record entry

to the multiple overflowed bits.

With PEBS record format encoding 0011b, offset 90H reports the “applicable counter” field, which is a multi-

counter PEBS resolution index allowing software to correlate the PEBS record entry with the eventing PEBS over-

flow when multiple counters are configured to record PEBS records. Additionally, offset C0H captures a snapshot of

the TSC that provides a time line annotation for each PEBS record entry.

18.13.1.2 PEBS Events

The list of precise events supported for PEBS in the Skylake microarchitecture is shown in Table 18-56.

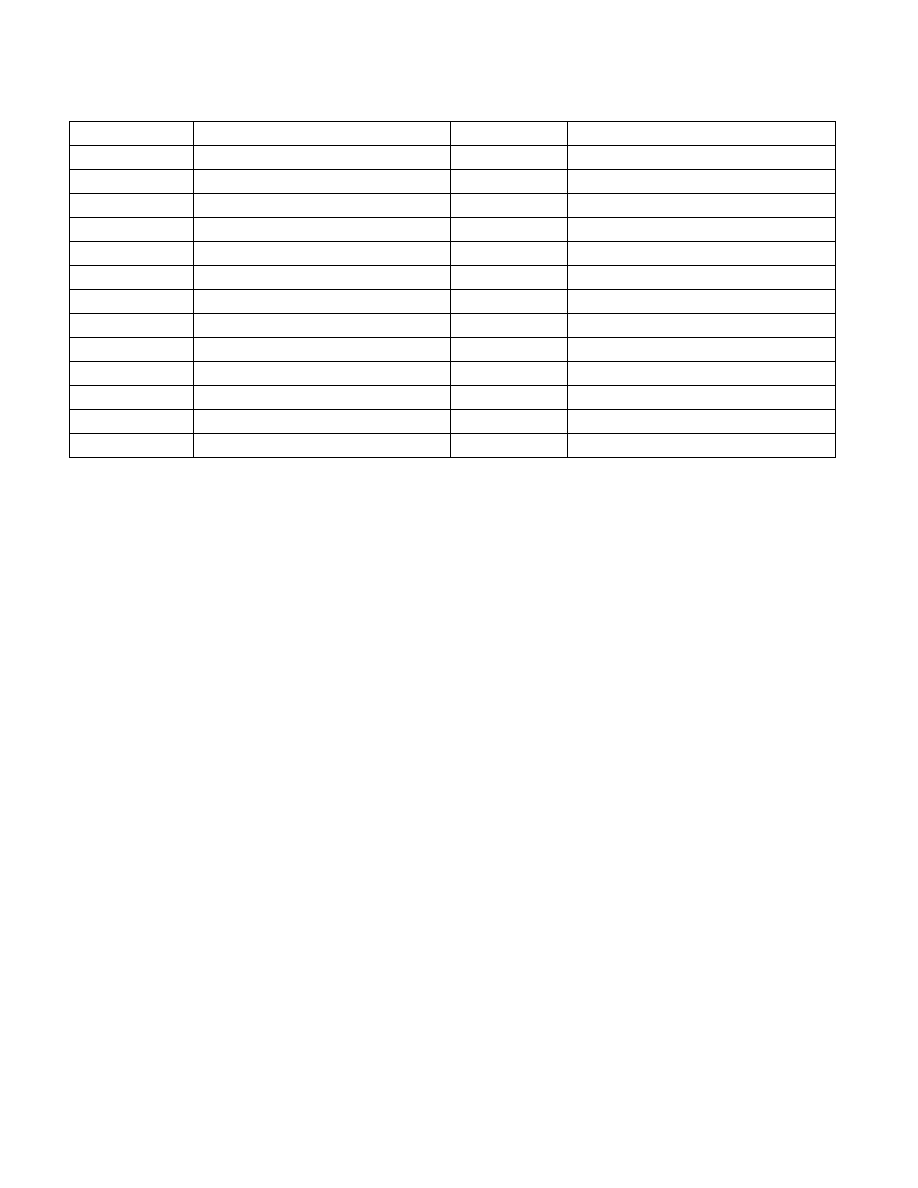

Table 18-55. PEBS Record Format for 6th Generation Intel Core Processor Family

Byte Offset

Field

Byte Offset

Field

00H

R/EFLAGS

68H

R11

08H

R/EIP

70H

R12

10H

R/EAX

78H

R13

18H

R/EBX

80H

R14

20H

R/ECX

88H

R15

28H

R/EDX

90H

Applicable Counter

30H

R/ESI

98H

Data Linear Address

38H

R/EDI

A0H

Data Source Encoding

40H

R/EBP

A8H

Latency value (core cycles)

48H

R/ESP

B0H

EventingIP

50H

R8

B8H

TX Abort Information (Section 18.11.5.1)

58H

R9

C0H

TSC

60H

R10