18-72 Vol. 3B

PERFORMANCE MONITORING

Additionally, there is also a fixed counter, counting uncore clockticks, for the uncore domain. Table 18-39 summa-

rizes the number MSRs for uncore PMU for each box.

The uncore performance events for the C-Box and ARB units are listed in Table 19-9.

18.11.7 Intel

®

Xeon

®

Processor E5 v3 Family Uncore Performance Monitoring Facility

Details of the uncore performance monitoring facility of Intel Xeon Processor E5 v3 families are available in “Intel®

Xeon® Processor E5 v3 Uncore Performance Monitoring Programming Reference Manual”. The MSR-based uncore

PMU interfaces are listed in Table 35-31.

18.12 INTEL

®

CORE

™

M PROCESSOR PERFORMANCE MONITORING FACILITY

The Intel

®

Core™ M processor and the 5th Generation Intel Core processor families are based on the Broadwell

microarchitecture. The core PMU supports architectural performance monitoring capability with version ID 3 (see

Section 18.2.3) and a host of non-architectural monitoring capabilities.

Architectural performance monitoring version 3 capabilities are described in Section 18.2.3.

The core PMU has the same capability as those described in Section 18.11. IA32_PERF_GLOBAL_STATUS provide a

bit indicator (bit 55) for PMI handler to distinguish PMI due to output buffer overflow condition due to accumulating

packet data from Intel Processor Trace.

Table 18-52. Uncore PMU MSR Summary

Box

# of Boxes

Counters per

Box

Counter

Width

General

Purpose

Global

Enable Comment

C-Box

SKU specific

2

44

Yes

Per-box

Up to 4, seeTable 35-19

MSR_UNC_CBO_CONFIG

ARB

1

2

44

Yes

Uncore

Fixed Counter

N.A.

N.A.

48

No

Uncore

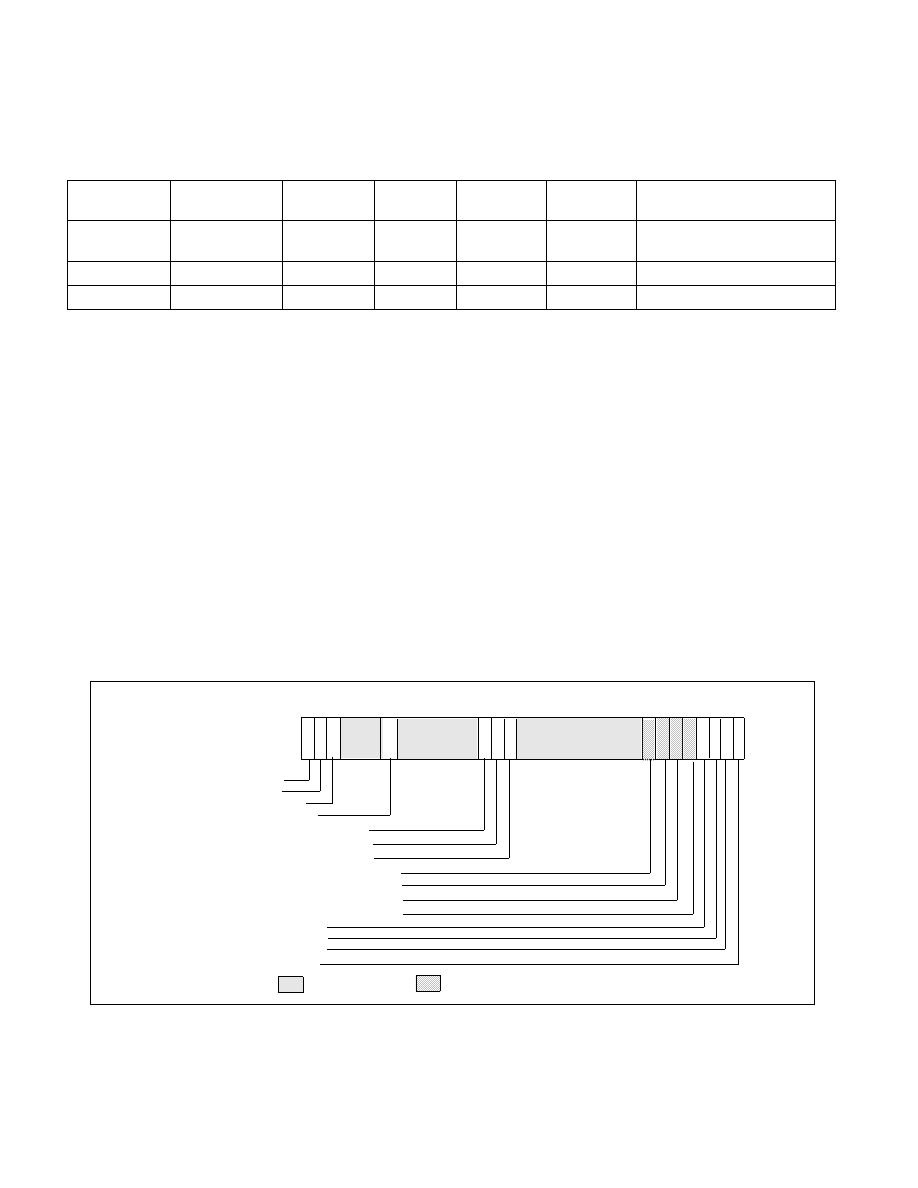

Figure 18-41. IA32_PERF_GLOBAL_STATUS MSR in Broadwell Microarchitecture

62

FIXED_CTR2 Overflow (RO)

FIXED_CTR1 Overflow (RO)

FIXED_CTR0 Overflow (RO)

PMC7_OVF (RO, If PMC7 present)

2 1 0

PMC6_OVF (RO, If PMC6 present)

31

32

33

34

35

Reserved

63

CondChgd

Ovf_Buffer

8 7 6 5 4 3

PMC5_OVF (RO, If PMC5 present)

PMC4_OVF (RO, If PMC4 present)

PMC3_OVF (RO)

PMC2_OVF (RO)

PMC1_OVF (RO)

PMC0_OVF (RO)

Valid if CPUID.0AH:EAX[15:8] = 8; else reserved

Ovf_UncorePMU

61

Trace_ToPA_PMI

55