19-32 Vol. 3B

PERFORMANCE-MONITORING EVENTS

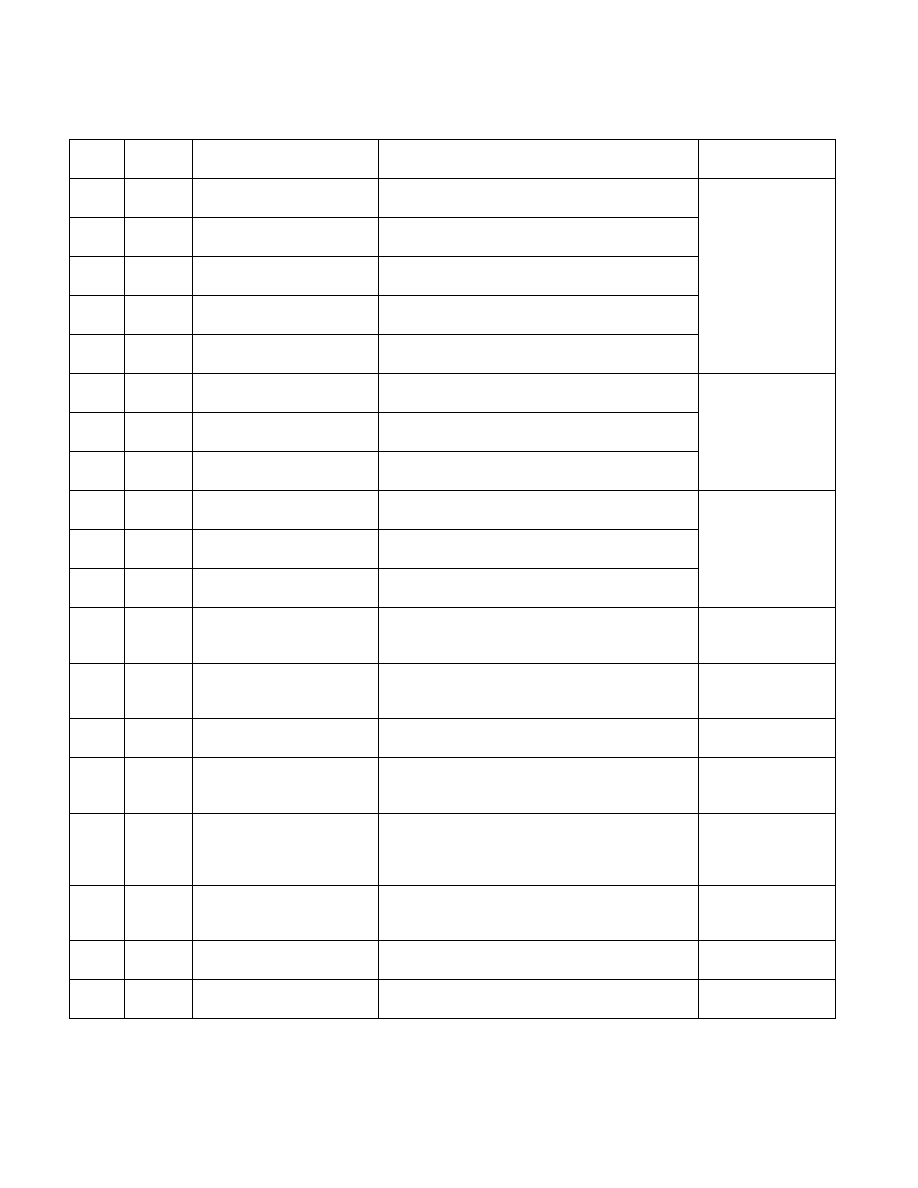

Table 19-9. Non-Architectural Uncore Performance Events in the 4th Generation Intel® Core™ Processors

Event

Num.

1

Umask

Value

Event Mask Mnemonic

Description

Comment

22H

01H

UNC_CBO_XSNP_RESPONSE.M

ISS

A snoop misses in some processor core.

Must combine with

one of the umask

values of 20H, 40H,

80H.

22H

02H

UNC_CBO_XSNP_RESPONSE.I

NVAL

A snoop invalidates a non-modified line in some

processor core.

22H

04H

UNC_CBO_XSNP_RESPONSE.H

IT

A snoop hits a non-modified line in some processor

core.

22H

08H

UNC_CBO_XSNP_RESPONSE.H

ITM

A snoop hits a modified line in some processor core.

22H

10H

UNC_CBO_XSNP_RESPONSE.I

NVAL_M

A snoop invalidates a modified line in some processor

core.

22H

20H

UNC_CBO_XSNP_RESPONSE.E

XTERNAL_FILTER

Filter on cross-core snoops initiated by this Cbox due

to external snoop request.

Must combine with at

least one of 01H, 02H,

04H, 08H, 10H.

22H

40H

UNC_CBO_XSNP_RESPONSE.X

CORE_FILTER

Filter on cross-core snoops initiated by this Cbox due

to processor core memory request.

22H

80H

UNC_CBO_XSNP_RESPONSE.E

VICTION_FILTER

Filter on cross-core snoops initiated by this Cbox due

to L3 eviction.

34H

01H

UNC_CBO_CACHE_LOOKUP.M

L3 lookup request that access cache and found line in

M-state.

Must combine with

one of the umask

values of 10H, 20H,

40H, 80H.

34H

06H

UNC_CBO_CACHE_LOOKUP.ES L3 lookup request that access cache and found line in E

or S state.

34H

08H

UNC_CBO_CACHE_LOOKUP.I

L3 lookup request that access cache and found line in I-

state.

34H

10H

UNC_CBO_CACHE_LOOKUP.RE

AD_FILTER

Filter on processor core initiated cacheable read

requests. Must combine with at least one of 01H, 02H,

04H, 08H.

34H

20H

UNC_CBO_CACHE_LOOKUP.WR

ITE_FILTER

Filter on processor core initiated cacheable write

requests. Must combine with at least one of 01H, 02H,

04H, 08H.

34H

40H

UNC_CBO_CACHE_LOOKUP.EX

TSNP_FILTER

Filter on external snoop requests. Must combine with

at least one of 01H, 02H, 04H, 08H.

34H

80H

UNC_CBO_CACHE_LOOKUP.AN

Y_REQUEST_FILTER

Filter on any IRQ or IPQ initiated requests including

uncacheable, non-coherent requests. Must combine

with at least one of 01H, 02H, 04H, 08H.

80H

01H

UNC_ARB_TRK_OCCUPANCY.A

LL

Counts cycles weighted by the number of requests

waiting for data returning from the memory controller.

Accounts for coherent and non-coherent requests

initiated by IA cores, processor graphic units, or L3.

Counter 0 only.

81H

01H

UNC_ARB_TRK_REQUEST.ALL Counts the number of coherent and in-coherent

requests initiated by IA cores, processor graphic units,

or L3.

81H

20H

UNC_ARB_TRK_REQUEST.WRI

TES

Counts the number of allocated write entries, include

full, partial, and L3 evictions.

81H

80H

UNC_ARB_TRK_REQUEST.EVIC

TIONS

Counts the number of L3 evictions allocated.