18-62 Vol. 3B

PERFORMANCE MONITORING

Additionally, there is also a fixed counter, counting uncore clockticks, for the uncore domain. Table 18-39 summa-

rizes the number MSRs for uncore PMU for each box.

18.9.6.1 Uncore Performance Monitoring Events

There are certain restrictions on the uncore performance counters in each C-Box. Specifically,

•

Occupancy events are supported only with counter 0 but not counter 1.

Other uncore C-Box events can be programmed with either counter 0 or 1.

The C-Box uncore performance events described in Table 19-16 can collect performance characteristics of transac-

tions initiated by processor core. In that respect, they are similar to various sub-events in the

OFFCORE_RESPONSE family of performance events in the core PMU. Information such as data supplier locality

(LLC HIT/MISS) and snoop responses can be collected via OFFCORE_RESPONSE and qualified on a per-thread

basis.

On the other hand, uncore performance event logic can not associate its counts with the same level of per-thread

qualification attributes as the core PMU events can. Therefore, whenever similar event programming capabilities

are available from both core PMU and uncore PMU, the recommendation is that utilizing the core PMU events may

be less affected by artifacts, complex interactions and other factors.

18.9.7 Intel

®

Xeon

®

Processor E5 Family Performance Monitoring Facility

The Intel

®

Xeon

®

Processor E5 Family (and Intel

®

Core™ i7-3930K Processor) are based on Intel microarchitec-

ture code name Sandy Bridge-E. While the processor cores share the same microarchitecture as those of the Intel

®

Xeon

®

Processor E3 Family and 2nd generation Intel Core i7-2xxx, Intel Core i5-2xxx, Intel Core i3-2xxx processor

series, the uncore subsystems are different. An overview of the uncore performance monitoring facilities of the

Intel Xeon processor E5 family (and Intel Core i7-3930K processor) is described in Section 18.9.8.

Thus, the performance monitoring facilities in the processor core generally are the same as those described in

Section 18.9 through Section 18.9.5. However, the MSR_OFFCORE_RSP_0/MSR_OFFCORE_RSP_1 Response

Supplier Info field shown in Table 18-37 applies to Intel Core Processors with CPUID signature of

DisplayFamily_DisplayModel encoding of 06_2AH; Intel Xeon processor with CPUID signature of

DisplayFamily_DisplayModel encoding of 06_2DH supports an additional field for remote DRAM controller shown in

Table 18-40. Additionally, the are some small differences in the non-architectural performance monitoring events

(see Table 19-14).

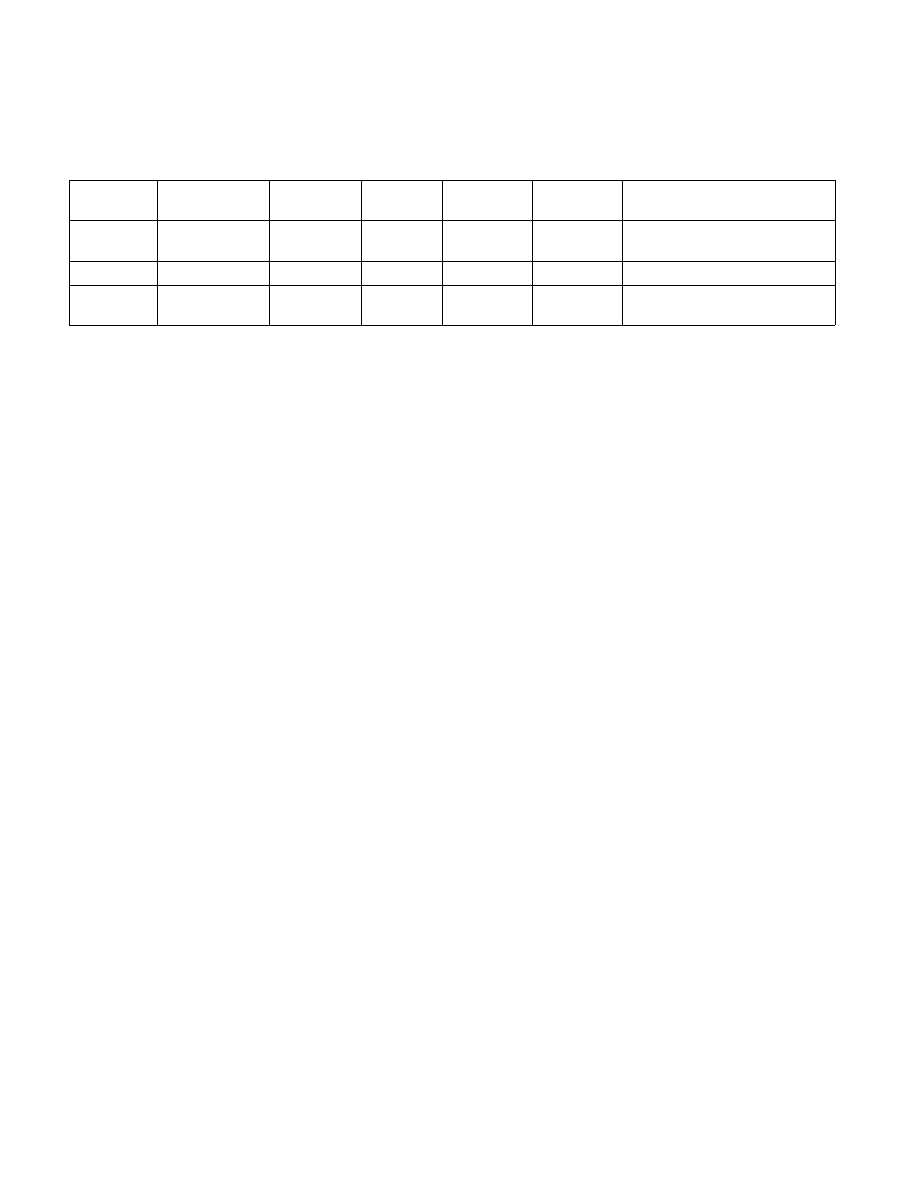

Table 18-39. Uncore PMU MSR Summary

Box

# of Boxes

Counters per

Box

Counter

Width

General

Purpose

Global

Enable Comment

C-Box

SKU specific

2

44

Yes

Per-box

Up to 4, seeTable 35-19

MSR_UNC_CBO_CONFIG

ARB

1

2

44

Yes

Uncore

Fixed

Counter

N.A.

N.A.

48

No

Uncore