Vol. 3B 17-27

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

17.7

LAST BRANCH, INTERRUPT, AND EXCEPTION RECORDING FOR

PROCESSORS BASED ON INTEL® MICROARCHITECTURE CODE NAME

NEHALEM

The processors based on Intel

®

microarchitecture code name Nehalem and Intel

®

microarchitecture code name

Westmere support last branch interrupt and exception recording. These capabilities are similar to those found in

Intel Core 2 processors and adds additional capabilities:

•

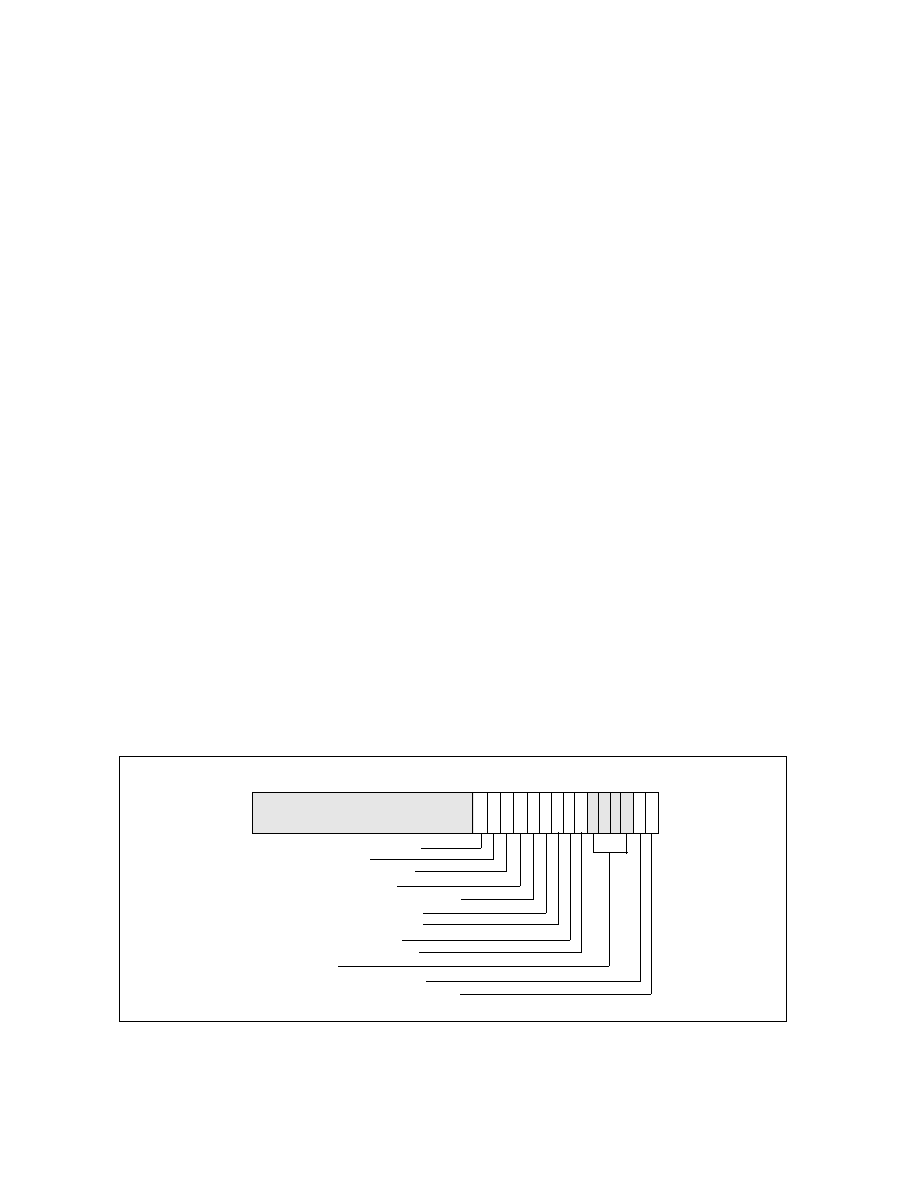

Debug Trace and Branch Recording Control — The IA32_DEBUGCTL MSR provides bit fields for software to

configure mechanisms related to debug trace, branch recording, branch trace store, and performance counter

operations. See Section 17.4.1 for a description of the flags. See Figure 17-11 for the MSR layout.

•

Last branch record (LBR) stack — There are 16 MSR pairs that store the source and destination addresses

related to recently executed branches. See Section 17.7.1.

•

Monitoring and single-stepping of branches, exceptions, and interrupts — See Section 17.4.2 and

Section 17.4.3. In addition, the ability to freeze the LBR stack on a PMI request is available.

•

Branch trace messages — The IA32_DEBUGCTL MSR provides bit fields for software to enable each logical

processor to generate branch trace messages. See Section 17.4.4. However, not all BTM messages are

observable using the Intel

®

QPI link.

•

Last exception records — See Section 17.11.3.

•

Branch trace store and CPL-qualified BTS — See Section 17.4.6 and Section 17.4.5.

•

FREEZE_LBRS_ON_PMI flag (bit 11) — see Section 17.4.7 for legacy Freeze_LBRs_On_PMI operation.

•

FREEZE_PERFMON_ON_PMI flag (bit 12) — see Section 17.4.7 for legacy Freeze_Perfmon_On_PMI

operation.

•

UNCORE_PMI_EN (bit 13) — When set. this logical processor is enabled to receive an counter overflow

interrupt form the uncore.

•

FREEZE_WHILE_SMM_EN (bit 14) — FREEZE_WHILE_SMM_EN is supported if

IA32_PERF_CAPABILITIES.FREEZE_WHILE_SMM[Bit 12] is reporting 1. See Section 17.4.1.

Processors based on Intel microarchitecture code name Nehalem provide additional capabilities:

•

Independent control of uncore PMI — The IA32_DEBUGCTL MSR provides a bit field (see Figure 17-11) for

software to enable each logical processor to receive an uncore counter overflow interrupt.

•

LBR filtering — Processors based on Intel microarchitecture code name Nehalem support filtering of LBR

based on combination of CPL and branch type conditions. When LBR filtering is enabled, the LBR stack only

captures the subset of branches that are specified by MSR_LBR_SELECT.

Figure 17-11. IA32_DEBUGCTL MSR for Processors based

on Intel microarchitecture code name Nehalem

31

TR — Trace messages enable

BTINT — Branch trace interrupt

BTF — Single-step on branches

LBR — Last branch/interrupt/exception

Reserved

8 7 6 5 4 3 2 1 0

BTS — Branch trace store

Reserved

9

10

BTS_OFF_OS — BTS off in OS

BTS_OFF_USR — BTS off in user code

FREEZE_LBRS_ON_PMI

FREEZE_PERFMON_ON_PMI

11

12

14

FREEZE_WHILE_SMM_EN

UNCORE_PMI_EN

13