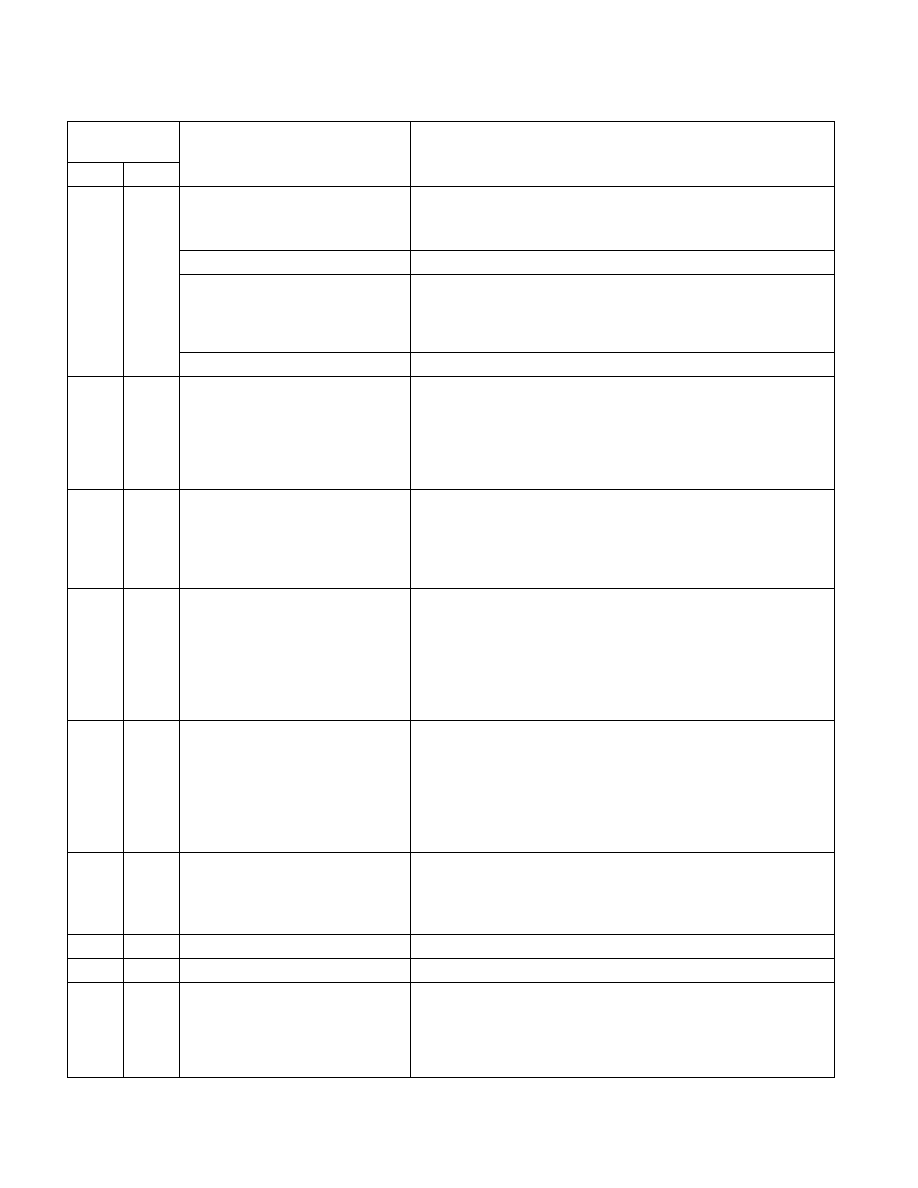

35-318 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

16

Enhanced Intel SpeedStep Technology Enable (R/W)

1 = Enhanced Intel SpeedStep Technology enabled.

On the Pentium M processor, this bit may be configured to be read-only.

22:17

Reserved.

23

xTPR Message Disable (R/W)

When set to 1, xTPR messages are disabled. xTPR messages are optional

messages that allow the processor to inform the chipset of its priority.

The default is processor specific.

63:24

Reserved.

1C9H

457

MSR_LASTBRANCH_TOS

Last Branch Record Stack TOS (R/W)

Contains an index (bits 0-3) that points to the MSR containing the most

recent branch record. See also:

• MSR_LASTBRANCH_0_FROM_IP (at 40H)

• Section 17.13, “Last Branch, Interrupt, and Exception Recording

1D9H

473

MSR_DEBUGCTLB

Debug Control (R/W)

Controls how several debug features are used. Bit definitions are

discussed in the referenced section.

See Section 17.13, “Last Branch, Interrupt, and Exception Recording

1DDH

477

MSR_LER_TO_LIP

Last Exception Record To Linear IP (R)

This area contains a pointer to the target of the last branch instruction

that the processor executed prior to the last exception that was

generated or the last interrupt that was handled.

See Section 17.13, “Last Branch, Interrupt, and Exception Recording

(Pentium M Processors)” and Section 17.14.2, “Last Branch and Last

1DEH

478

MSR_LER_FROM_LIP

Last Exception Record From Linear IP (R)

Contains a pointer to the last branch instruction that the processor

executed prior to the last exception that was generated or the last

interrupt that was handled.

See Section 17.13, “Last Branch, Interrupt, and Exception Recording

(Pentium M Processors)” and Section 17.14.2, “Last Branch and Last

2FFH

767

IA32_MTRR_DEF_TYPE

Default Memory Types (R/W)

Sets the memory type for the regions of physical memory that are not

mapped by the MTRRs.

See Section 11.11.2.1, “IA32_MTRR_DEF_TYPE MSR.”

400H

1024

IA32_MC0_CTL

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

401H

1025

IA32_MC0_STATUS

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

402H

1026

IA32_MC0_ADDR

See Section 14.3.2.3., “IA32_MCi_ADDR MSRs”.

The IA32_MC0_ADDR register is either not implemented or contains no

address if the ADDRV flag in the IA32_MC0_STATUS register is clear.

When not implemented in the processor, all reads and writes to this MSR

will cause a general-protection exception.

Table 35-45. MSRs in Pentium M Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec