11-22 Vol. 3A

MEMORY CACHE CONTROL

•

VCNT (variable range registers count) field, bits 0 through 7 — Indicates the number of variable ranges

implemented on the processor.

•

FIX (fixed range registers supported) flag, bit 8 — Fixed range MTRRs (IA32_MTRR_FIX64K_00000

through IA32_MTRR_FIX4K_0F8000) are supported when set; no fixed range registers are supported when

clear.

•

WC (write combining) flag, bit 10 — The write-combining (WC) memory type is supported when set; the

WC type is not supported when clear.

•

SMRR (System-Management Range Register) flag, bit 11 — The system-management range register

(SMRR) interface is supported when bit 11 is set; the SMRR interface is not supported when clear.

Bit 9 and bits 12 through 63 in the IA32_MTRRCAP MSR are reserved. If software attempts to write to the

IA32_MTRRCAP MSR, a general-protection exception (#GP) is generated.

Software must read IA32_MTRRCAP VCNT field to determine the number of variable MTRRs and query other

feature bits in IA32_MTRRCAP to determine additional capabilities that are supported in a processor. For example,

some processors may report a value of ‘8’ in the VCNT field, other processors may report VCNT with different

values.

11.11.2 Setting

Memory

Ranges with MTRRs

The memory ranges and the types of memory specified in each range are set by three groups of registers: the

IA32_MTRR_DEF_TYPE MSR, the fixed-range MTRRs, and the variable range MTRRs. These registers can be read

and written to using the RDMSR and WRMSR instructions, respectively. The IA32_MTRRCAP MSR indicates the

availability of these registers on the processor (see Section 11.11.1, “MTRR Feature Identification”).

11.11.2.1 IA32_MTRR_DEF_TYPE MSR

The IA32_MTRR_DEF_TYPE MSR (named MTRRdefType MSR for the P6 family processors) sets the default proper-

ties of the regions of physical memory that are not encompassed by MTRRs. The functions of the flags and field in

this register are as follows:

•

Type field, bits 0 through 7 — Indicates the default memory type used for those physical memory address

ranges that do not have a memory type specified for them by an MTRR (see Table 11-8 for the encoding of this

field). The legal values for this field are 0, 1, 4, 5, and 6. All other values result in a general-protection

exception (#GP) being generated.

Intel recommends the use of the UC (uncached) memory type for all physical memory addresses where

memory does not exist. To assign the UC type to nonexistent memory locations, it can either be specified as the

default type in the Type field or be explicitly assigned with the fixed and variable MTRRs.

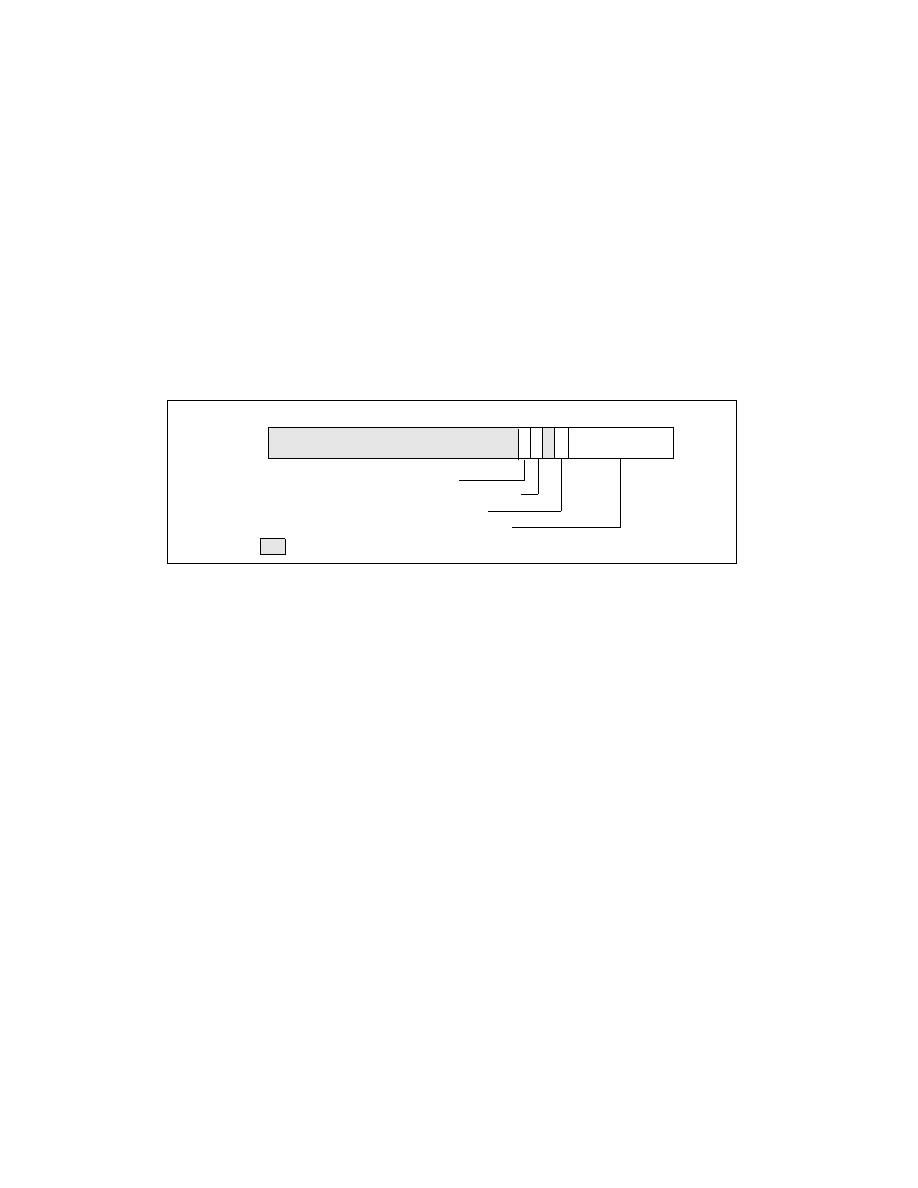

Figure 11-5. IA32_MTRRCAP Register

VCNT — Number of variable range registers

FIX — Fixed range registers supported

WC — Write-combining memory type supported

63

0

Reserved

W

C

7

10

11

VCNT

F

I

X

8

9

Reserved

SMRR — SMRR interface supported