Vol. 3C 35-285

MODEL-SPECIFIC REGISTERS (MSRS)

63:0

Registers R8-15 (and the associated state-save

MSRs) exist only in Intel 64 processors. These

registers contain valid information only when the

processor is operating in 64-bit mode at the time

of the error.

196H

406

MSR_MCG_R14

0, 1, 2, 3,

4, 6

Unique

Machine Check R14

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Registers R8-15 (and the associated state-save

MSRs) exist only in Intel 64 processors. These

registers contain valid information only when the

processor is operating in 64-bit mode at the time

of the error.

197H

407

MSR_MCG_R15

0, 1, 2, 3,

4, 6

Unique

Machine Check R15

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Registers R8-15 (and the associated state-save

MSRs) exist only in Intel 64 processors. These

registers contain valid information only when the

processor is operating in 64-bit mode at the time

of the error.

198H

408

IA32_PERF_STATUS

3, 4, 6

Unique

See Table 35-2. See Section 14.1, “Enhanced Intel

199H

409

IA32_PERF_CTL

3, 4, 6

Unique

See Table 35-2. See Section 14.1, “Enhanced Intel

19AH

410

IA32_CLOCK_MODULATION

0, 1, 2, 3,

4, 6

Unique

Thermal Monitor Control (R/W)

See Table 35-2.

See Section 14.7.3, “Software Controlled Clock

19BH

411

IA32_THERM_INTERRUPT

0, 1, 2, 3,

4, 6

Unique

Thermal Interrupt Control (R/W)

See Section 14.7.2, “Thermal Monitor,” and see

19CH

412

IA32_THERM_STATUS

0, 1, 2, 3,

4, 6

Shared

Thermal Monitor Status (R/W)

See Section 14.7.2, “Thermal Monitor,” and see

19DH

413

MSR_THERM2_CTL

Thermal Monitor 2 Control.

3,

Shared

For Family F, Model 3 processors: When read,

specifies the value of the target TM2 transition

last written. When set, it sets the next target

value for TM2 transition.

4, 6

Shared

For Family F, Model 4 and Model 6 processors:

When read, specifies the value of the target TM2

transition last written. Writes may cause #GP

exceptions.

1A0H

416

IA32_MISC_ENABLE

0, 1, 2, 3,

4, 6

Shared

Enable Miscellaneous Processor Features (R/W)

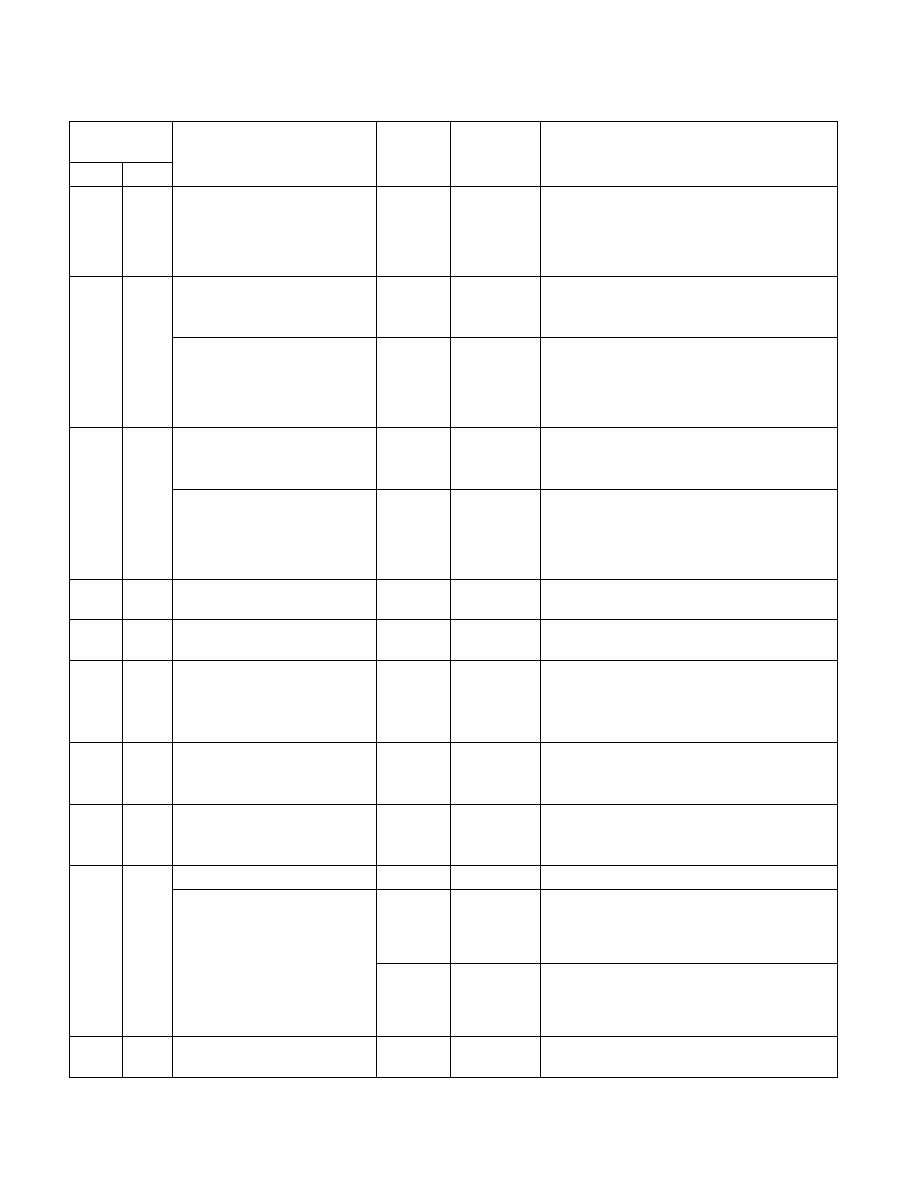

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec