Vol. 3B 15-11

MACHINE-CHECK ARCHITECTURE

•

Corrected error count threshold, bits 14:0 — Software must initialize this field. The value is compared with

the corrected error count field in IA32_MCi_STATUS, bits 38 through 52. An overflow event is signaled to the

CMCI LVT entry (see Table 10-1) in the APIC when the count value equals the threshold value. The new LVT

entry in the APIC is at 02F0H offset from the APIC_BASE. If CMCI interface is not supported for a particular

bank (but IA32_MCG_CAP[10] = 1), this field will always read 0.

•

CMCI_EN (Corrected error interrupt enable/disable/indicator), bits 30 — Software sets this bit to

enable the generation of corrected machine-check error interrupt (CMCI). If CMCI interface is not supported for

a particular bank (but IA32_MCG_CAP[10] = 1), this bit is writeable but will always return 0 for that bank. This

bit also indicates CMCI is supported or not supported in the corresponding bank. See Section 15.5 for details of

software detection of CMCI facility.

Some microarchitectural sub-systems that are the source of corrected MC errors may be shared by more than one

logical processors. Consequently, the facilities for reporting MC errors and controlling mechanisms may be shared

by more than one logical processors. For example, the IA32_MCi_CTL2 MSR is shared between logical processors

sharing a processor core. Software is responsible to program IA32_MCi_CTL2 MSR in a consistent manner with

CMCI delivery and usage.

After processor reset, IA32_MCi_CTL2 MSRs are zero’ed.

15.3.2.6 IA32_MCG Extended Machine Check State MSRs

The Pentium 4 and Intel Xeon processors implement a variable number of extended machine-check state MSRs.

The MCG_EXT_P flag in the IA32_MCG_CAP MSR indicates the presence of these extended registers, and the

MCG_EXT_CNT field indicates the number of these registers actually implemented. See Section 15.3.1.1,

“IA32_MCG_CAP MSR.” Also see Table 15-4.

In processors with support for Intel 64 architecture, 64-bit machine check state MSRs are aliased to the legacy

MSRs. In addition, there may be registers beyond IA32_MCG_MISC. These may include up to five reserved MSRs

(IA32_MCG_RESERVED[1:5]) and save-state MSRs for registers introduced in 64-bit mode. See Table 15-5.

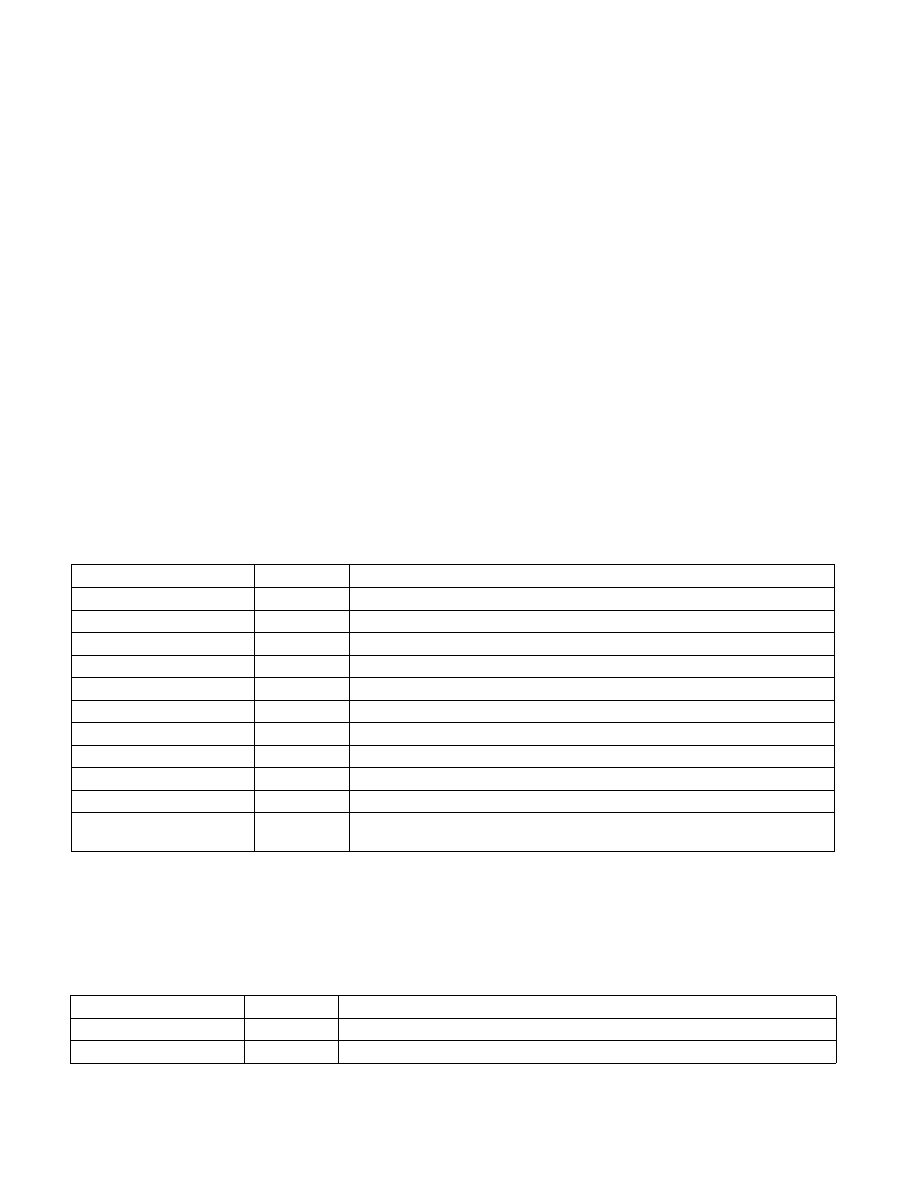

Table 15-4. Extended Machine Check State MSRs

in Processors Without Support for Intel 64 Architecture

MSR

Address

Description

IA32_MCG_EAX

180H

Contains state of the EAX register at the time of the machine-check error.

IA32_MCG_EBX

181H

Contains state of the EBX register at the time of the machine-check error.

IA32_MCG_ECX

182H

Contains state of the ECX register at the time of the machine-check error.

IA32_MCG_EDX

183H

Contains state of the EDX register at the time of the machine-check error.

IA32_MCG_ESI

184H

Contains state of the ESI register at the time of the machine-check error.

IA32_MCG_EDI

185H

Contains state of the EDI register at the time of the machine-check error.

IA32_MCG_EBP

186H

Contains state of the EBP register at the time of the machine-check error.

IA32_MCG_ESP

187H

Contains state of the ESP register at the time of the machine-check error.

IA32_MCG_EFLAGS

188H

Contains state of the EFLAGS register at the time of the machine-check error.

IA32_MCG_EIP

189H

Contains state of the EIP register at the time of the machine-check error.

IA32_MCG_MISC

18AH

When set, indicates that a page assist or page fault occurred during DS normal

operation.

Table 15-5. Extended Machine Check State MSRs

In Processors With Support For Intel 64 Architecture

MSR

Address

Description

IA32_MCG_RAX

180H

Contains state of the RAX register at the time of the machine-check error.

IA32_MCG_RBX

181H

Contains state of the RBX register at the time of the machine-check error.