35-206 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.12 MSRS IN INTEL

®

XEON

®

PROCESSOR E5 V3 AND E7 V3 PRODUCT FAMILY

Intel

®

Xeon

®

processor E5 v3 family and Intel

®

Xeon

®

processor E7 v3 family are based on Haswell-E microarchi-

tecture (CPUID DisplayFamily_DisplayModel = 06_3F). These processors supports the MSR interfaces listed in

Table 35-18, Table 35-27, and Table 35-30.

59:0

Package C10 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C10

states. Count at the same frequency as the TSC.

63:60

Reserved

See Table 35-18, Table 35-19, Table 35-20, Table 35-27, Table 35-28 for other MSR definitions applicable to processors with CPUID

signature 06_45H.

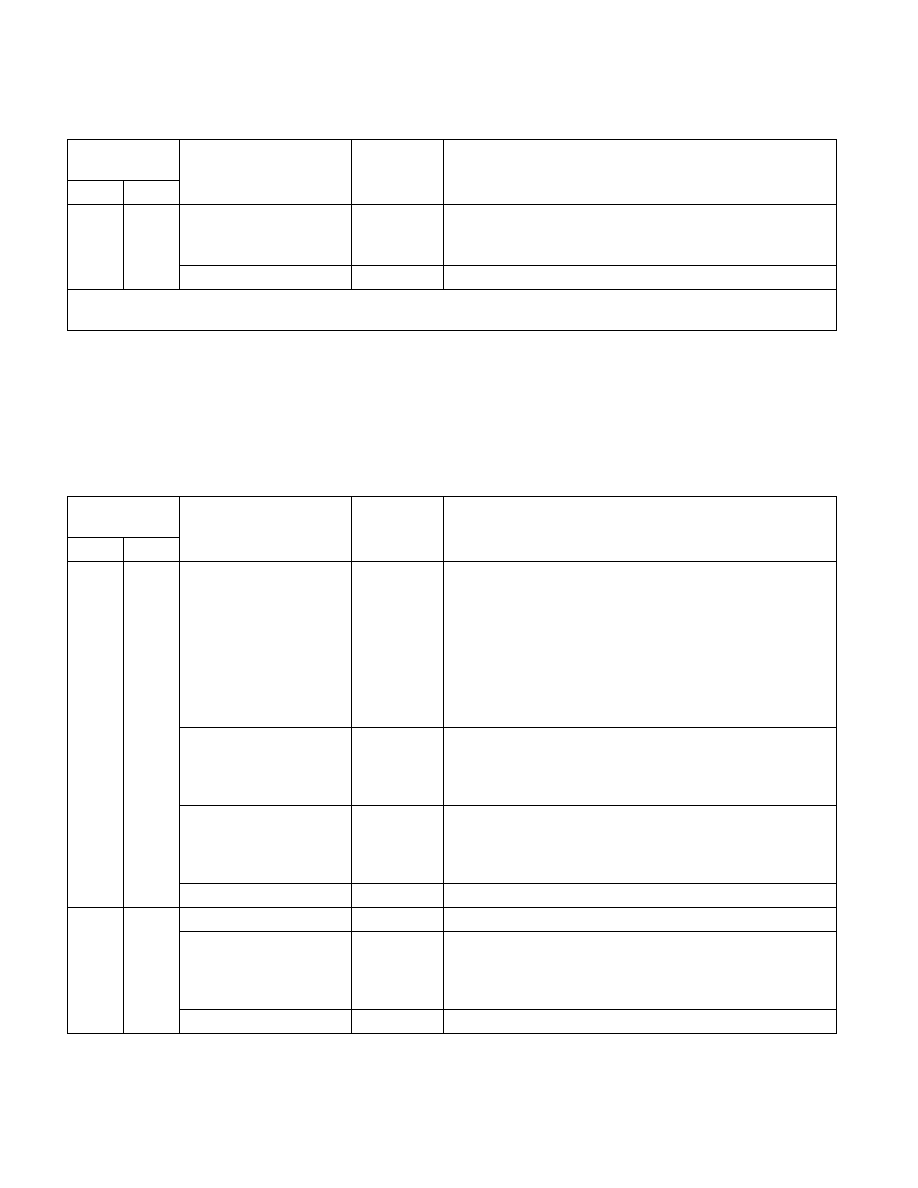

Table 35-30. Additional MSRs Supported by Intel® Xeon® Processor E5 v3 Family

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

35H

53

MSR_CORE_THREAD_COUN

T

Package

Configured State of Enabled Processor Core Count and Logical

Processor Count (RO)

• After a Power-On RESET, enumerates factory configuration of

the number of processor cores and logical processors in the

physical package.

• Following the sequence of (i) BIOS modified a Configuration Mask

which selects a subset of processor cores to be active post

RESET and (ii) a RESET event after the modification, enumerates

the current configuration of enabled processor core count and

logical processor count in the physical package.

15:0

Core_COUNT (RO)

The number of processor cores that are currently enabled (by

either factory configuration or BIOS configuration) in the physical

package.

31:16

THREAD_COUNT (RO)

The number of logical processors that are currently enabled (by

either factory configuration or BIOS configuration) in the physical

package.

63:32

Reserved

53H

83

MSR_THREAD_ID_INFO

Thread

A Hardware Assigned ID for the Logical Processor (RO)

7:0

Logical_Processor_ID (RO)

An implementation-specific numerical. value physically assigned to

each logical processor. This ID is not related to Initial APIC ID or

x2APIC ID, it is unique within a physical package.

63:8

Reserved

Table 35-29. Additional Residency MSRs Supported by 4th Generation Intel® Core™ Processors with

DisplayFamily_DisplayModel Signature 06_45H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec