35-106 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.6

MSRS IN THE INTEL

®

MICROARCHITECTURE CODE NAME NEHALEM

Table 35-13 lists model-specific registers (MSRs) that are common for Intel

®

microarchitecture code name

Nehalem. These include Intel Core i7 and i5 processor family. These processors have a CPUID signature with

DisplayFamily_DisplayModel of 06_1AH, 06_1EH, 06_1FH, 06_2EH, see Table 35-1. Additional MSRs specific to

06_1AH, 06_1EH, 06_1FH are listed in Table 35-14. Some MSRs listed in these tables are used by BIOS. More infor-

mation about these MSR can be found at http://biosbits.org.

The column “Scope” represents the package/core/thread scope of individual bit field of an MSR. “Thread” means

this bit field must be programmed on each logical processor independently. “Core” means the bit field must be

programmed on each processor core independently, logical processors in the same core will be affected by change

of this bit on the other logical processor in the same core. “Package” means the bit field must be programmed once

for each physical package. Change of a bit filed with a package scope will affect all logical processors in that phys-

ical package.

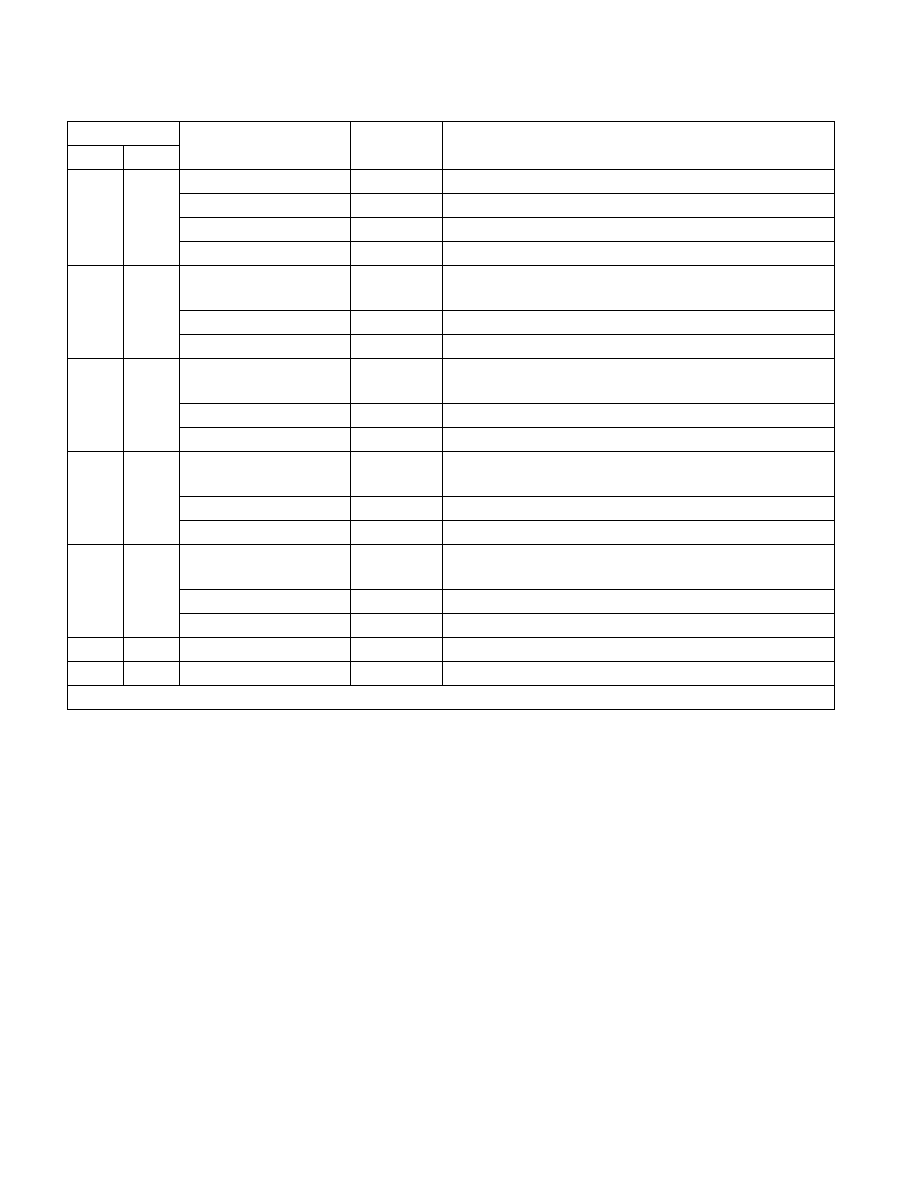

C8FH

3215

IA32_PQR_ASSOC

Core

Resource Association Register (R/W)

31:0

Reserved

33:32

COS (R/W).

63: 34

Reserved

D10H

3344

IA32_L2_QOS_MASK_0

Module

L2 Class Of Service Mask - COS 0 (R/W)

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0] >=0

0:7

CBM: Bit vector of available L2 ways for COS 0 enforcement

63:8

Reserved

D11H

3345

IA32_L2_QOS_MASK_1

Module

L2 Class Of Service Mask - COS 1 (R/W)

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0] >=1

0:7

CBM: Bit vector of available L2 ways for COS 0 enforcement

63:8

Reserved

D12H

3346

IA32_L2_QOS_MASK_2

Module

L2 Class Of Service Mask - COS 2 (R/W)

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0] >=2

0:7

CBM: Bit vector of available L2 ways for COS 0 enforcement

63:8

Reserved

D13H

3347

IA32_L2_QOS_MASK_3

Package

L2 Class Of Service Mask - COS 3 (R/W).

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0] >=3

0:19

CBM: Bit vector of available L2 ways for COS 3 enforcement

63:20

Reserved

D90H

3472

IA32_BNDCFGS

Core

See Table 35-2.

DA0H

3488

IA32_XSS

Core

See Table 35-6, and Table 35-12 for MSR definitions applicable to processors with CPUID signature 06_5CH.

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec