35-124 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.6.1 Additional MSRs in the Intel

®

Xeon

®

Processor 5500 and 3400 Series

Intel Xeon Processor 5500 and 3400 series support additional model-specific registers listed in Table 35-14. These

MSRs also apply to Intel Core i7 and i5 processor family CPUID signature with DisplayFamily_DisplayModel of

06_1AH, 06_1EH and 06_1FH, see Table 35-1.

C000_

0103H

IA32_TSC_AUX

Thread

AUXILIARY TSC Signature. (R/W) See Table 35-2 and Section

17.15.2, ŌĆ£IA32_TSC_AUX Register and RDTSCP Support.ŌĆØ

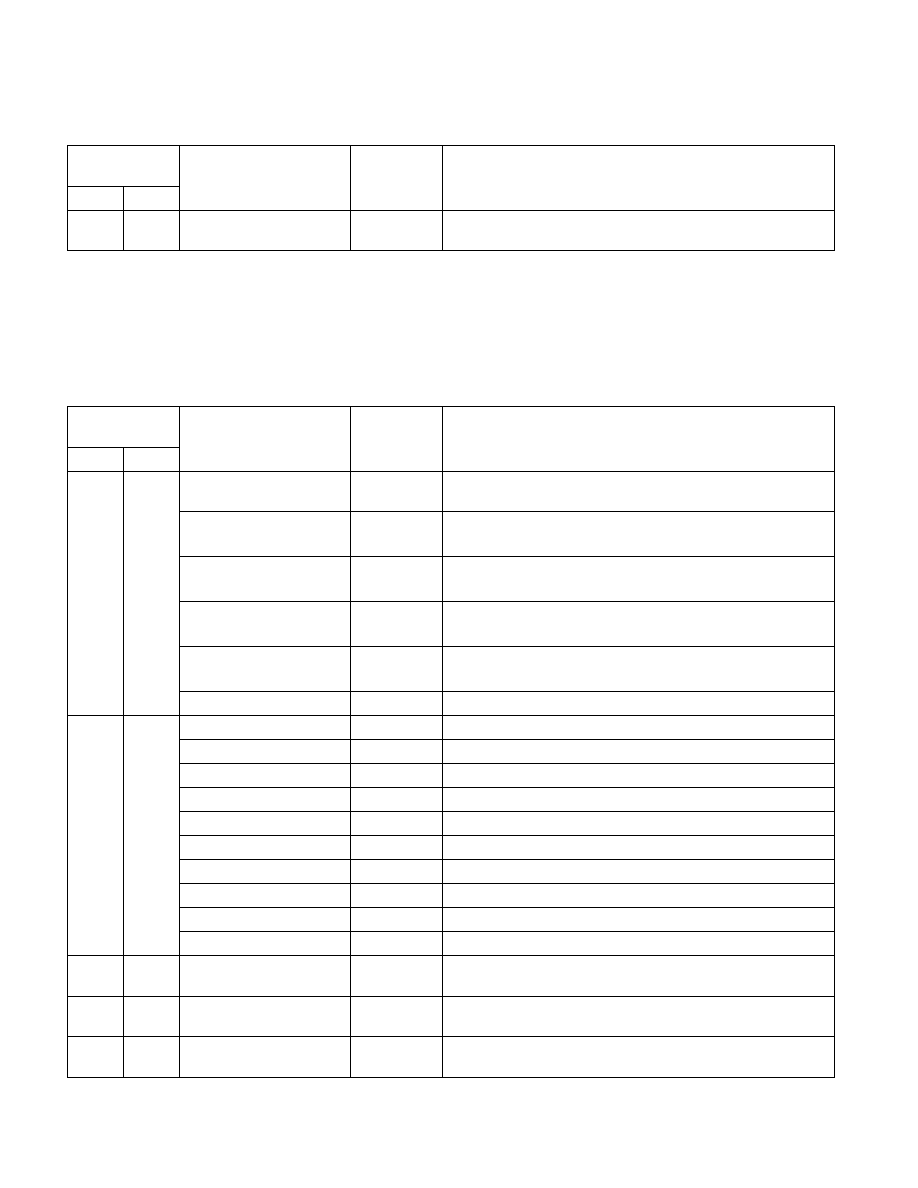

Table 35-14. Additional MSRs in Intel® Xeon® Processor 5500 and 3400 Series

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Actual maximum turbo frequency is multiplied by 133.33MHz. (not

available to model 06_2EH)

7:0

Maximum Turbo Ratio Limit 1C (R/O)

Maximum Turbo mode ratio limit with 1 core active.

15:8

Maximum Turbo Ratio Limit 2C (R/O)

Maximum Turbo mode ratio limit with 2cores active.

23:16

Maximum Turbo Ratio Limit 3C (R/O)

Maximum Turbo mode ratio limit with 3cores active.

31:24

Maximum Turbo Ratio Limit 4C (R/O)

Maximum Turbo mode ratio limit with 4 cores active.

63:32

Reserved.

301H

769

MSR_GQ_SNOOP_MESF

Package

0

From M to S (R/W)

1

From E to S (R/W)

2

From S to S (R/W)

3

From F to S (R/W)

4

From M to I (R/W)

5

From E to I (R/W)

6

From S to I (R/W)

7

From F to I (R/W)

63:8

Reserved.

391H

913

MSR_UNCORE_PERF_

GLOBAL_CTRL

Package

See Section 18.7.2.1, ŌĆ£Uncore Performance Monitoring

392H

914

MSR_UNCORE_PERF_

GLOBAL_STATUS

Package

See Section 18.7.2.1, ŌĆ£Uncore Performance Monitoring

393H

915

MSR_UNCORE_PERF_

GLOBAL_OVF_CTRL

Package

See Section 18.7.2.1, ŌĆ£Uncore Performance Monitoring

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec