35-86 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

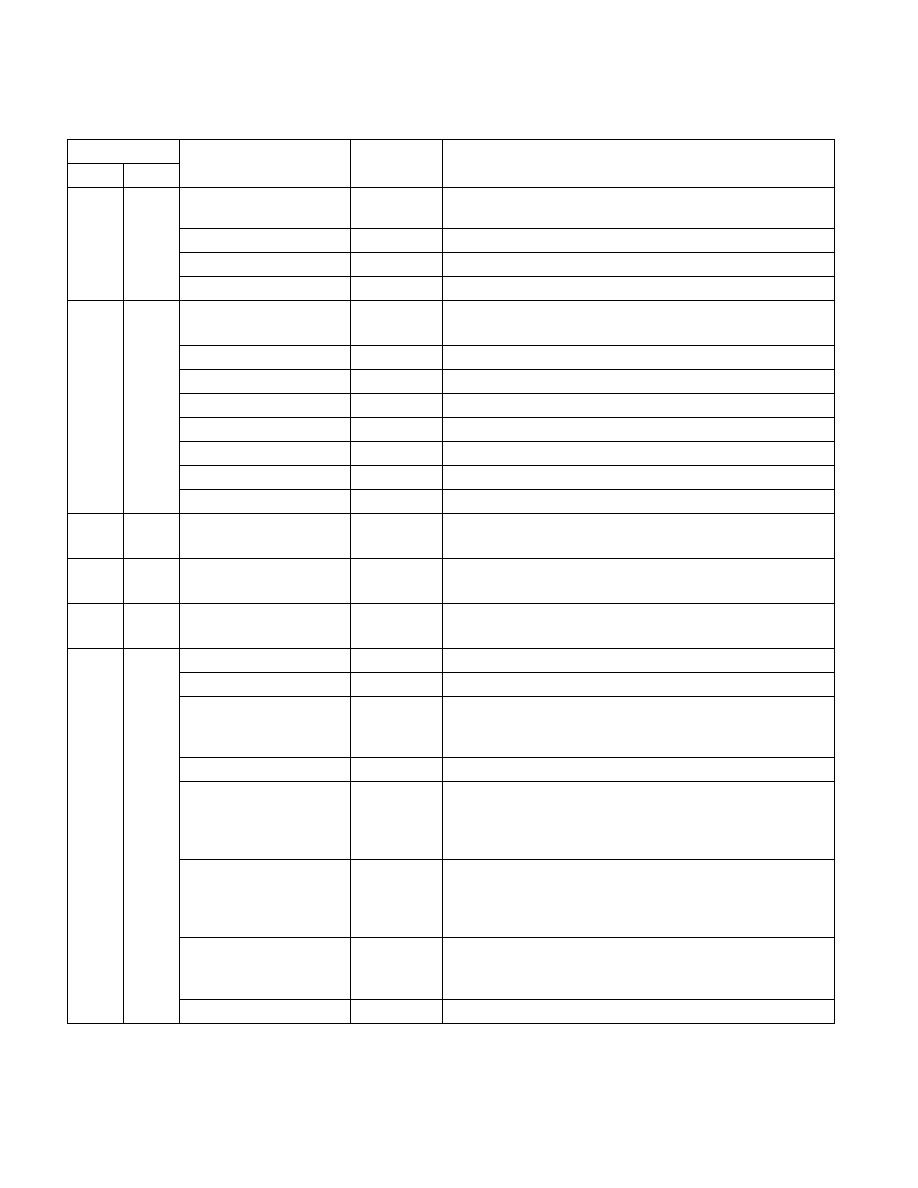

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture

Address

Register Name

Scope

Bit Description

Hex

Dec

17H

23

MSR_PLATFORM_ID

Module

Model Specific Platform ID (R)

49:0

Reserved.

52:50

See Table 35-2.

63:33

Reserved.

3AH

58

IA32_FEATURE_CONTROL

Core

Control Features in Intel 64Processor (R/W)

See Table 35-2.

0

Lock (R/WL)

1

Enable VMX inside SMX operation (R/WL)

2

Enable VMX outside SMX operation (R/WL)

14:8

SENTER local functions enables (R/WL)

15

SENTER global functions enable (R/WL)

18

SGX global functions enable (R/WL)

63:19

Reserved.

3BH

59

IA32_TSC_ADJUST

Core

Per-Core TSC ADJUST (R/W)

See Table 35-2.

C3H

195

IA32_PMC2

Core

Performance Counter Register

See Table 35-2.

C4H

196

IA32_PMC3

Core

Performance Counter Register

See Table 35-2.

CEH

206

MSR_PLATFORM_INFO

Package

See http://biosbits.org.

7:0

Reserved.

15:8

Package

Maximum Non-Turbo Ratio (R/O)

The is the ratio of the frequency that invariant TSC runs at.

Frequency = ratio * 100 MHz.

27:16

Reserved.

28

Package

Programmable Ratio Limit for Turbo Mode (R/O)

When set to 1, indicates that Programmable Ratio Limits for Turbo

mode is enabled, and when set to 0, indicates Programmable Ratio

Limits for Turbo mode is disabled.

29

Package

Programmable TDP Limit for Turbo Mode (R/O)

When set to 1, indicates that TDP Limits for Turbo mode are

programmable, and when set to 0, indicates TDP Limit for Turbo

mode is not programmable.

30

Package

Programmable TJ OFFSET (R/O)

When set to 1, indicates that MSR_TEMPERATURE_TARGET.[27:24]

is valid and writable to specify an temperature offset.

39:31

Reserved.