35-68 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.4

MSRS IN INTEL PROCESSORS BASED ON SILVERMONT

MICROARCHITECTURE

Table 35-6 lists model-specific registers (MSRs) common to Intel processors based on the Silvermont microarchi-

tecture. These processors have a CPUID signature with DisplayFamily_DisplayModel of 06_37H, 06_4AH, 06_4DH,

06_5AH, and 06_5DH; see Table 35-1. The MSRs listed in Table 35-6 are also common to processors based on the

Airmont microarchitecture and newer microarchitectures for next generation Intel Atom processors.

Table 35-7 lists MSRs common to processors based on the Silvermont and Airmont microarchitectures, but not

newer microarchitectures.

Table 35-8, Table 35-9, and Table 35-10 lists MSRs that are model-specific across processors based on the Silver-

mont microarchitecture.

In the Silvermont microarchitecture, the scope column indicates the following: “Core” means each processor core

has a separate MSR, or a bit field not shared with another processor core. “Module” means the MSR or the bit field

is shared by a pair of processor cores in the physical package. “Package” means all processor cores in the physical

package share the same MSR or bit interface.

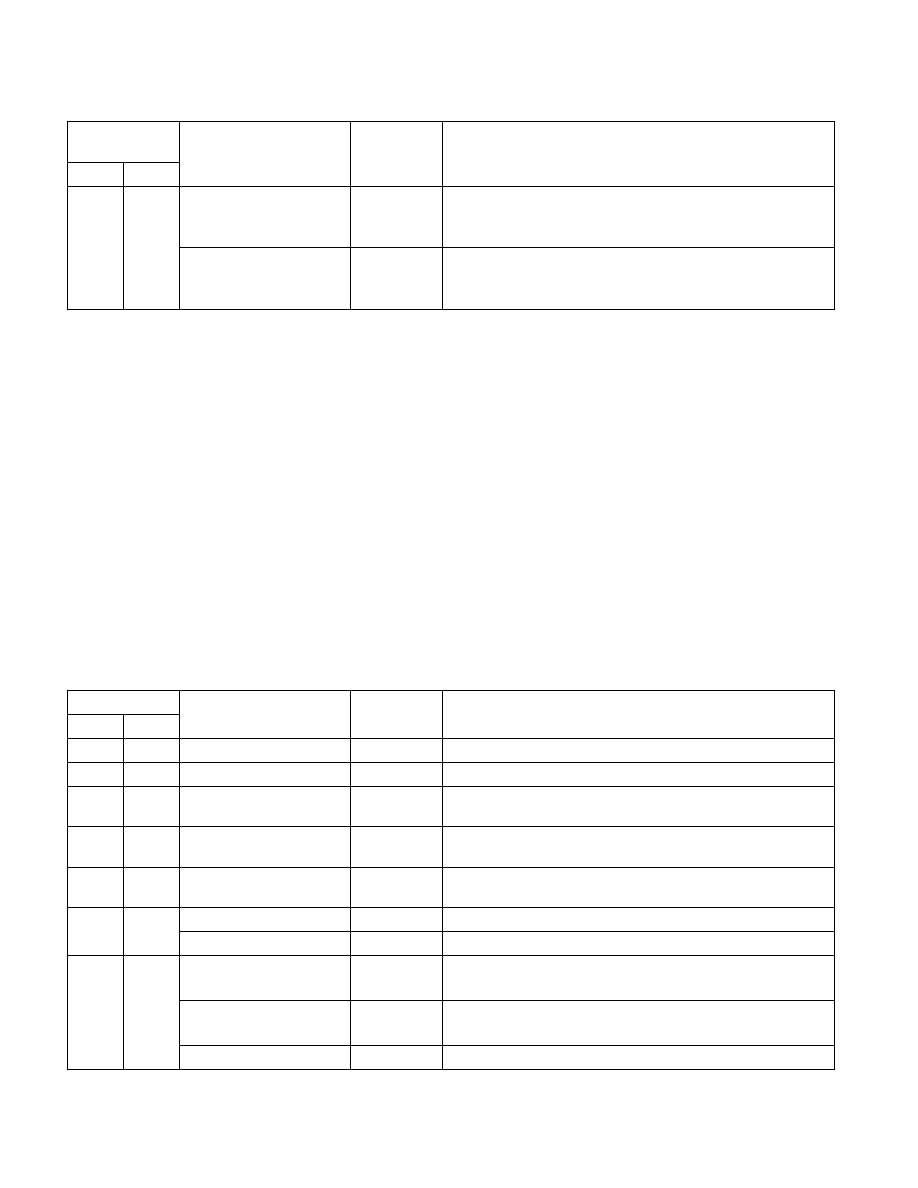

3FAH

1018

MSR_PKG_C6_RESIDENCY

Package

Package C6 Residency

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States

63:0

Package

Package C6 Residency Counter. (R/O)

Time that this package is in processor-specific C6 states since last

reset. Counts at 1 Mhz frequency.

Table 35-6. MSRs Common to the Silvermont Microarchitecture and Newer Microarchitectures for Intel Atom

Processors

Address

Register Name

Scope

Bit Description

Hex

Dec

0H

0

IA32_P5_MC_ADDR

Module

See Section 35.22, “MSRs in Pentium Processors.”

1H

1

IA32_P5_MC_TYPE

Module

See Section 35.22, “MSRs in Pentium Processors.”

6H

6

IA32_MONITOR_FILTER_

SIZE

Core

See Section 8.10.5, “Monitor/Mwait Address Range Determination.”

10H

16

IA32_TIME_STAMP_

COUNTER

Core

See Section 17.15, “Time-Stamp Counter,” and see Table 35-2.

1BH

27

IA32_APIC_BASE

Core

See Section 10.4.4, “Local APIC Status and Location,” and

2AH

42

MSR_EBL_CR_POWERON

Module

Processor Hard Power-On Configuration (R/W) Writes ignored.

63:0

Reserved (R/O)

34H

52

MSR_SMI_COUNT

Core

SMI Counter (R/O)

31:0

SMI Count (R/O)

Running count of SMI events since last RESET.

63:32

Reserved.

Table 35-5. MSRs Supported by Intel® Atom™ Processors (Contd.)with CPUID Signature 06_27H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec