35-328 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.22 MSRS IN PENTIUM PROCESSORS

The following MSRs are defined for the Pentium processors. The P5_MC_ADDR, P5_MC_TYPE, and TSC MSRs

(named IA32_P5_MC_ADDR, IA32_P5_MC_TYPE, and IA32_TIME_STAMP_COUNTER in the Pentium 4 processor)

are architectural; that is, code that accesses these registers will run on Pentium 4 and P6 family processors without

generating exceptions (see Section 35.1, ÔÇťArchitectural MSRsÔÇŁ). The CESR, CTR0, and CTR1 MSRs are unique to

Pentium processors; code that accesses these registers will generate exceptions on Pentium 4 and P6 family

processors.

35.23 MSR

INDEX

MSRs of recent processors are indexed here for convenience. IA32 MSRs are excluded from this index.

40EH

1038

MC4_ADDR

Defined in MCA architecture but not implemented in P6 Family processors.

40FH

1039

MC4_MISC

Defined in MCA architecture but not implemented in the P6 family

processors.

410H

1040

MC3_CTL

411H

1041

MC3_STATUS

Bit definitions same as MC0_STATUS.

412H

1042

MC3_ADDR

413H

1043

MC3_MISC

Defined in MCA architecture but not implemented in the P6 family

processors.

NOTES

1. Bit 0 of this register has been redefined several times, and is no longer used in P6 family processors.

2. The processor number feature may be disabled by setting bit 21 of the BBL_CR_CTL MSR (model-specific register address 119h) to

ÔÇť1ÔÇŁ. Once set, bit 21 of the BBL_CR_CTL may not be cleared. This bit is write-once. The processor number feature will be disabled

until the processor is reset.

3. The Pentium III processor will prevent FSB frequency overclocking with a new shutdown mechanism. If the FSB frequency selected

is greater than the internal FSB frequency the processor will shutdown. If the FSB selected is less than the internal FSB frequency

the BIOS may choose to use bit 11 to implement its own shutdown policy.

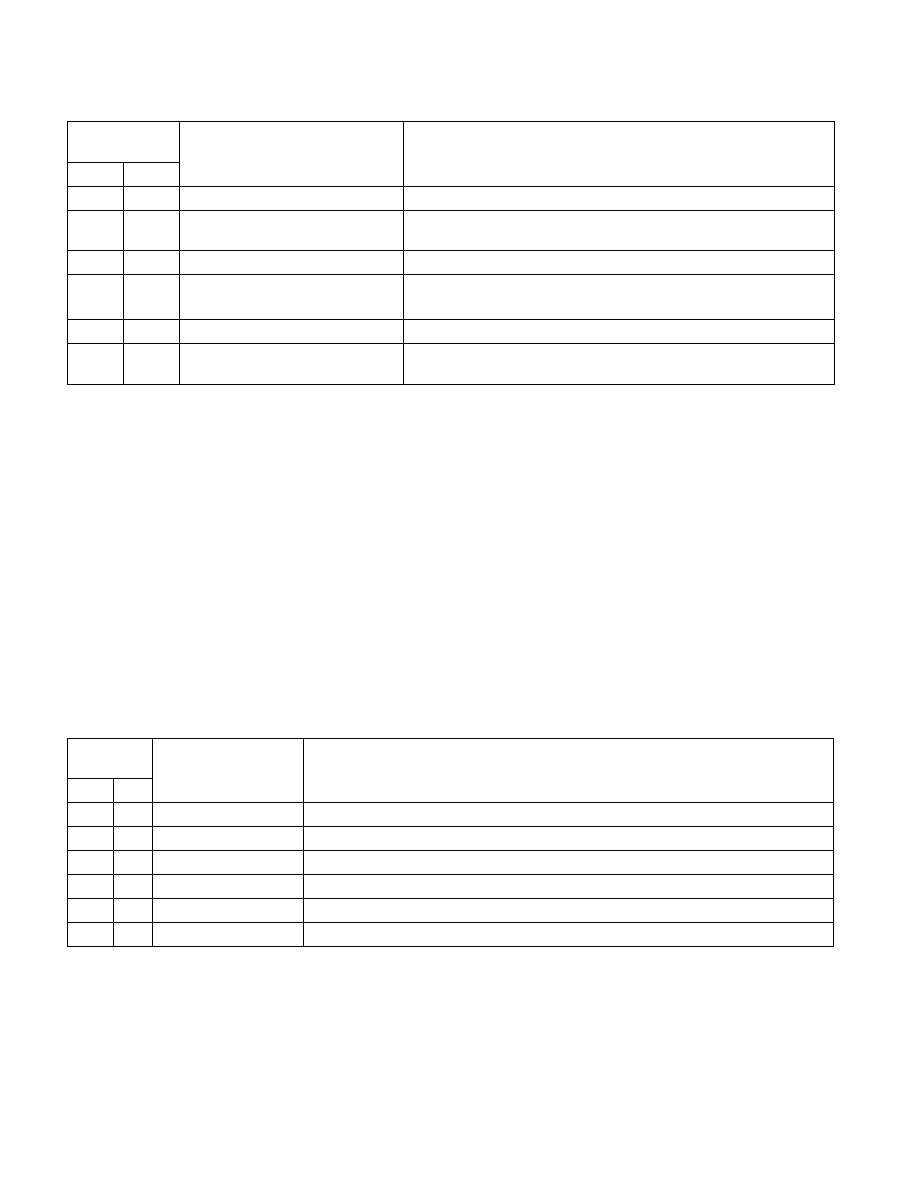

Table 35-47. MSRs in the Pentium Processor

Register

Address

Hex

Dec

Register Name

Bit Description

0H

0

P5_MC_ADDR

See Section 15.10.2, ÔÇťPentium

Processor Machine-Check Exception Handling.ÔÇŁ

1H

1

P5_MC_TYPE

See Section 15.10.2, ÔÇťPentium

Processor Machine-Check Exception Handling.ÔÇŁ

10H

16

TSC

See Section 17.15, ÔÇťTime-Stamp Counter.ÔÇŁ

11H

17

CESR

See Section 18.20.1, ÔÇťControl and Event Select Register (CESR).ÔÇŁ

12H

18

CTR0

Section 18.20.3, ÔÇťEvents Counted.ÔÇŁ

13H

19

CTR1

Section 18.20.3, ÔÇťEvents Counted.ÔÇŁ

Table 35-46. MSRs in the P6 Family Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec