35-76 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

Table 35-7 lists model-specific registers (MSRs) that are common to Intel

®

Atom™ processors based on the Silver-

mont and Airmont microarchitectures but not newer microarchitectures.

C000_

0101H

IA32_GS_BASE

Core

Map of BASE Address of GS (R/W)

See Table 35-2.

C000_

0102H

IA32_KERNEL_GSBASE

Core

Swap Target of BASE Address of GS (R/W) See Table 35-2.

C000_

0103H

IA32_TSC_AUX

Core

AUXILIARY TSC Signature. (R/W) See Table 35-2

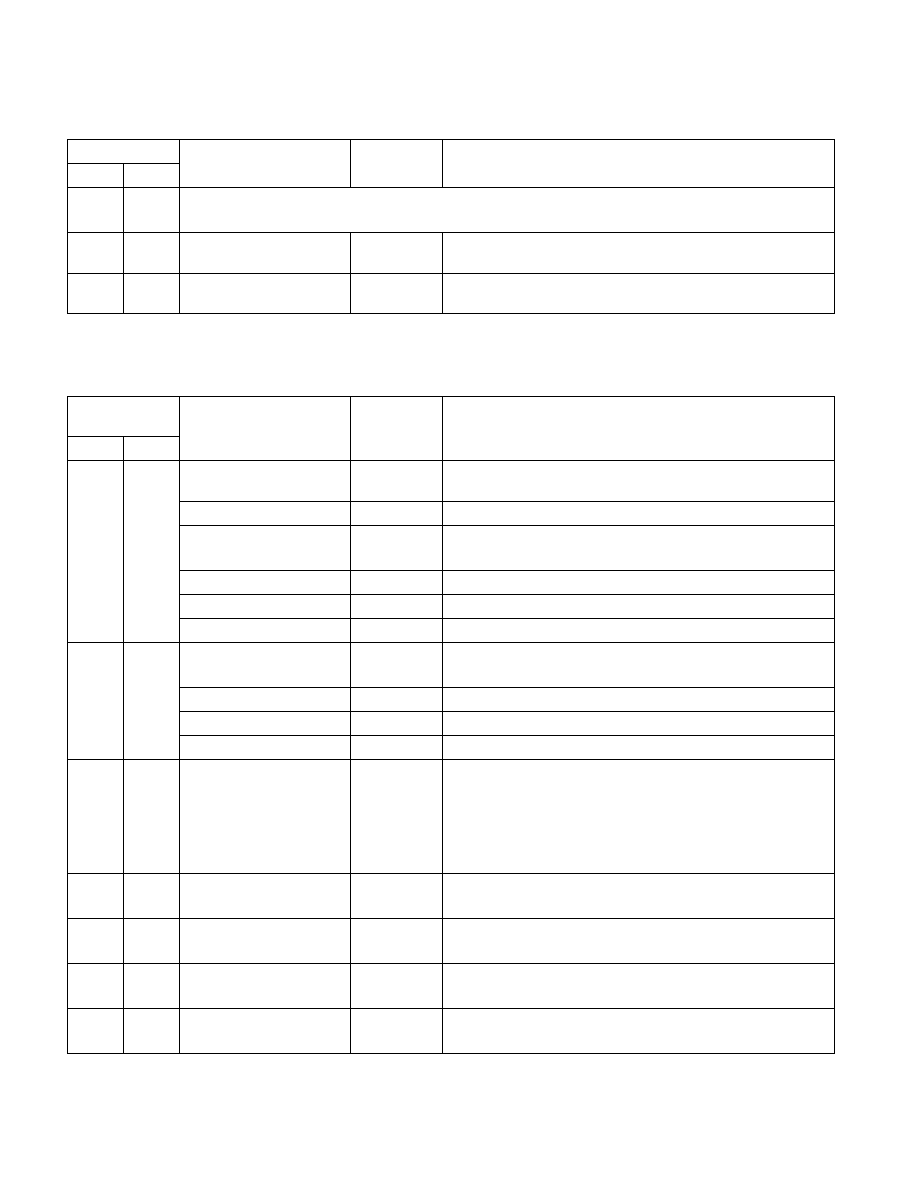

Table 35-7. MSRs Common to the Silvermont and Airmont Microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

17H

23

MSR_PLATFORM_ID

Module

Model Specific Platform ID (R)

7:0

Reserved.

12:8

Maximum Qualified Ratio (R)

The maximum allowed bus ratio.

49:13

Reserved.

52:50

63:33

Reserved.

3AH

58

IA32_FEATURE_CONTROL

Core

Control Features in Intel 64Processor (R/W)

See Table 35-2.

0

Lock (R/WL)

1

Reserved

2

Enable VMX outside SMX operation (R/WL)

40H

64

MSR_

LASTBRANCH_0_FROM_IP

Core

Last Branch Record 0 From IP (R/W)

One of eight pairs of last branch record registers on the last branch

record stack. The From_IP part of the stack contains pointers to

the source instruction. See also:

• Last Branch Record Stack TOS at 1C9H

• Section 17.5 and record format in Section 17.4.8.1

41H

65

MSR_

LASTBRANCH_1_FROM_IP

Core

Last Branch Record 1 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

42H

66

MSR_

LASTBRANCH_2_FROM_IP

Core

Last Branch Record 2 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

43H

67

MSR_

LASTBRANCH_3_FROM_IP

Core

Last Branch Record 3 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

44H

68

MSR_

LASTBRANCH_4_FROM_IP

Core

Last Branch Record 4 From IP (R/W)

See description of MSR_LASTBRANCH_0_FROM_IP.

Table 35-6. MSRs Common to the Silvermont Microarchitecture and Newer Microarchitectures for Intel Atom

Processors

Address

Register Name

Scope

Bit Description

Hex

Dec