Vol. 3C 35-43

MODEL-SPECIFIC REGISTERS (MSRS)

35.2

MSRS IN THE INTEL

®

CORE

™

2 PROCESSOR FAMILY

Table 35-3 lists model-specific registers (MSRs) for Intel Core 2 processor family and for Intel Xeon processors

based on Intel Core microarchitecture, architectural MSR addresses are also included in Table 35-3. These proces-

sors have a CPUID signature with DisplayFamily_DisplayModel of 06_0FH, see Table 35-1.

MSRs listed in Table 35-2 and Table 35-3 are also supported by processors based on the Enhanced Intel Core

microarchitecture. Processors based on the Enhanced Intel Core microarchitecture have the CPUID signature

DisplayFamily_DisplayModel of 06_17H.

The column “Shared/Unique” applies to multi-core processors based on Intel Core microarchitecture. “Unique”

means each processor core has a separate MSR, or a bit field in an MSR governs only a core independently.

“Shared” means the MSR or the bit field in an MSR address governs the operation of both processor cores.

NOTES:

1. In processors based on Intel NetBurst® microarchitecture, MSR addresses 180H-197H are supported, software must treat them as

model-specific. Starting with Intel Core Duo processors, MSR addresses 180H-185H, 188H-197H are reserved.

2. The *_ADDR MSRs may or may not be present; this depends on flag settings in IA32_MCi_STATUS. See Section 15.3.2.3 and Section

15.3.2.4 for more information.

3. MAXPHYADDR is reported by CPUID.80000008H:EAX[7:0].

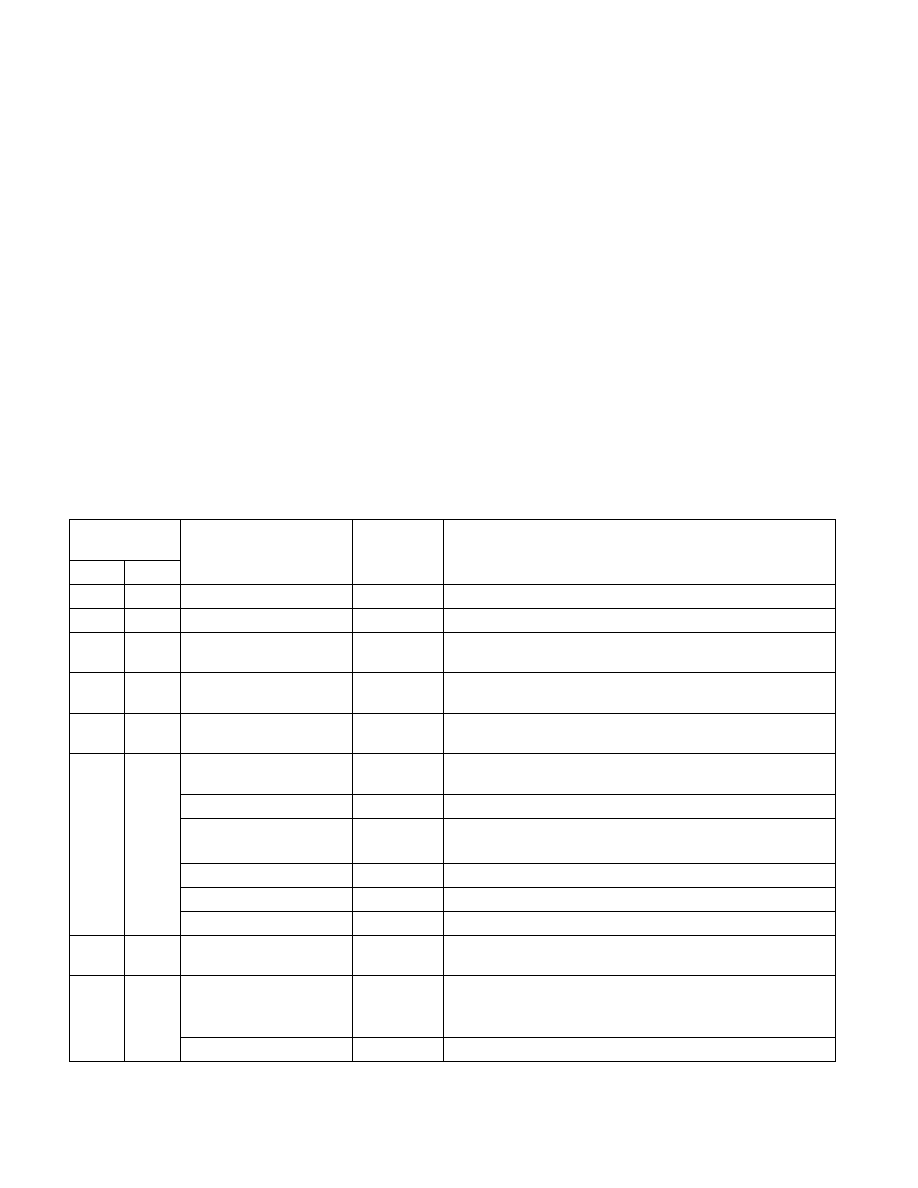

Table 35-3. MSRs in Processors Based on Intel® Core™ Microarchitecture

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec

0H

0

IA32_P5_MC_ADDR

Unique

See Section 35.22, “MSRs in Pentium Processors.”

1H

1

IA32_P5_MC_TYPE

Unique

See Section 35.22, “MSRs in Pentium Processors.”

6H

6

IA32_MONITOR_FILTER_SIZ

E

Unique

See Section 8.10.5, “Monitor/Mwait Address Range Determination.”

andTable 35-2.

10H

16

IA32_TIME_STAMP_COUNT

ER

Unique

See Section 17.15, “Time-Stamp Counter,” and see Table 35-2.

17H

23

IA32_PLATFORM_ID

Shared

Platform ID (R)

17H

23

MSR_PLATFORM_ID

Shared

Model Specific Platform ID (R)

7:0

Reserved.

12:8

Maximum Qualified Ratio (R)

The maximum allowed bus ratio.

49:13

Reserved.

52:50

See Table 35-2.

63:53

Reserved.

1BH

27

IA32_APIC_BASE

Unique

See Section 10.4.4, “Local APIC Status and Location.” and

2AH

42

MSR_EBL_CR_POWERON

Shared

Processor Hard Power-On Configuration (R/W)

Enables and disables processor features; (R) indicates current

processor configuration.

0

Reserved.