4-2 Vol. 3A

PAGING

•

If CR0.PG = 1, CR4.PAE = 1, and IA32_EFER.LME = 1, IA-32e paging is used.

1

IA-32e paging is detailed in

Section 4.5. IA-32e paging uses CR0.WP, CR4.PGE, CR4.PCIDE, CR4.SMEP, CR4.SMAP, CR4.PKE, and

IA32_EFER.NXE as described in Section 4.1.3. IA-32e paging is available only on processors that support the

Intel 64 architecture.

The three paging modes differ with regard to the following details:

•

Linear-address width. The size of the linear addresses that can be translated.

•

Physical-address width. The size of the physical addresses produced by paging.

•

Page size. The granularity at which linear addresses are translated. Linear addresses on the same page are

translated to corresponding physical addresses on the same page.

•

Support for execute-disable access rights. In some paging modes, software can be prevented from fetching

instructions from pages that are otherwise readable.

•

Support for PCIDs. With IA-32e paging, software can enable a facility by which a logical processor caches

information for multiple linear-address spaces. The processor may retain cached information when software

switches between different linear-address spaces.

•

Support for protection keys. With IA-32e paging, software can enable a facility by which each linear address is

associated with a protection key. Software can use a new control register to determine, for each protection

keys, how software can access linear addresses associated with that protection key.

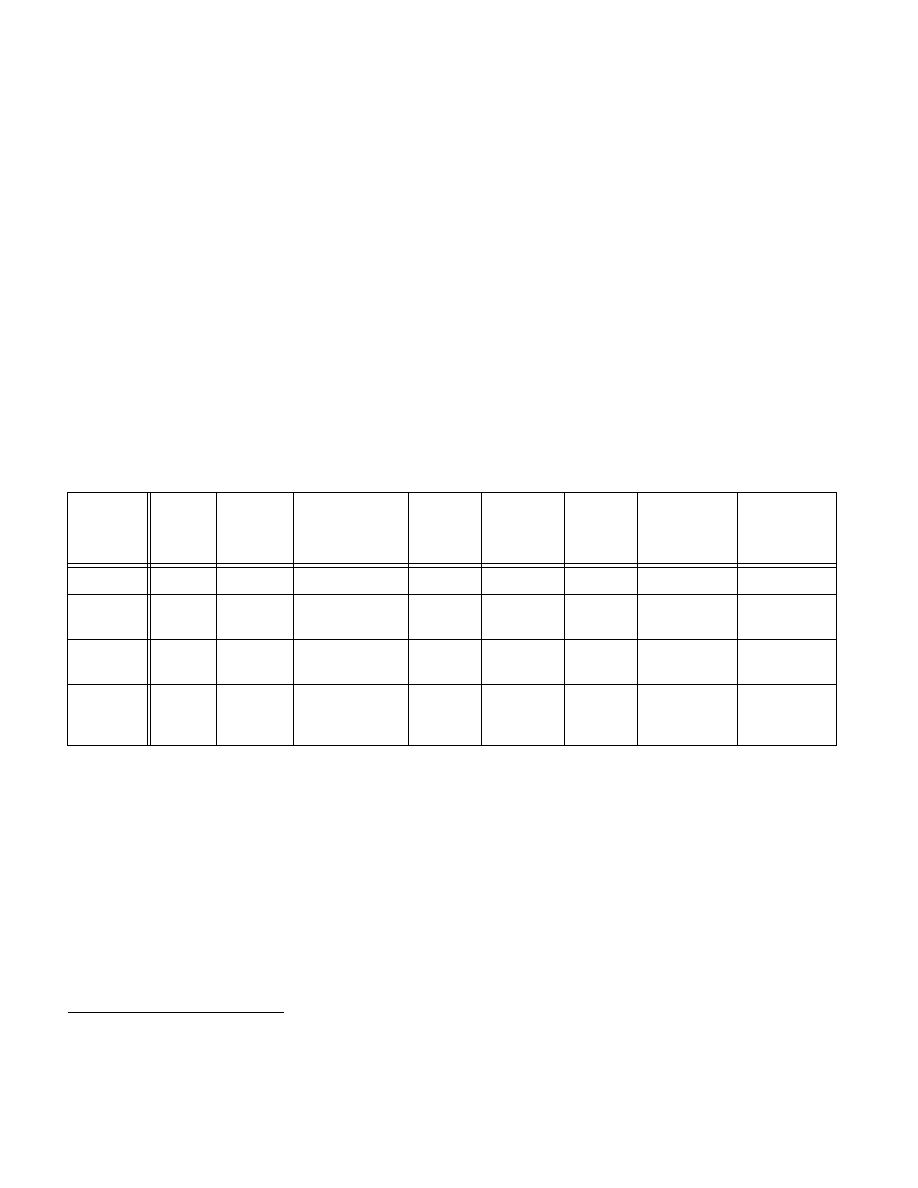

Table 4-1 illustrates the principal differences between the three paging modes.

Because they are used only if IA32_EFER.LME = 0, 32-bit paging and PAE paging are used only in legacy protected

mode. Because legacy protected mode cannot produce linear addresses larger than 32 bits, 32-bit paging and PAE

paging translate 32-bit linear addresses.

1. The LMA flag in the IA32_EFER MSR (bit 10) is a status bit that indicates whether the logical processor is in IA-32e mode (and thus

using IA-32e paging). The processor always sets IA32_EFER.LMA to CR0.PG & IA32_EFER.LME. Software cannot directly modify

IA32_EFER.LMA; an execution of WRMSR to the IA32_EFER MSR ignores bit 10 of its source operand.

Table 4-1. Properties of Different Paging Modes

Paging

Mode

PG in

CR0

PAE in

CR4

LME in

IA32_EFER

Lin.-

Addr.

Width

Phys.-

Addr.

Width

1

NOTES:

1. The physical-address width is always bounded by MAXPHYADDR; see Section 4.1.4.

Page

Sizes

Supports

Execute-

Disable?

Supports

PCIDs and

protection

keys?

None

0

N/A

N/A

32

32

N/A

No

No

32-bit

1

0

0

2

2. The processor ensures that IA32_EFER.LME must be 0 if CR0.PG = 1 and CR4.PAE = 0.

32

Up to

40

3

3. 32-bit paging supports physical-address widths of more than 32 bits only for 4-MByte pages and only if the PSE-36 mechanism is

supported; see Section 4.1.4 and Section 4.3.

4 KB

4 MB

4

4. 4-MByte pages are used with 32-bit paging only if CR4.PSE = 1; see Section 4.3.

No

No

PAE

1

1

0

32

Up to

52

4 KB

2 MB

Yes

5

5. Execute-disable access rights are applied only if IA32_EFER.NXE = 1; see Section 4.6.

No

IA-32e

1

1

1

48

Up to

52

4 KB

2 MB

1 GB

6

6. Not all processors that support IA-32e paging support 1-GByte pages; see Section 4.1.4.

Yes

Yes

7

7. PCIDs are used only if CR4.PCIDE = 1; see Section 4.10.1. Protection keys are used only if certain conditions hold; see Section 4.6.2.