Vol. 3A 4-7

PAGING

32-bit paging supports 4-MByte pages if CR4.PSE = 1. PAE paging and IA-32e paging support 2-MByte pages

(regardless of the value of CR4.PSE). IA-32e paging may support 1-GByte pages (see Section 4.1.4).

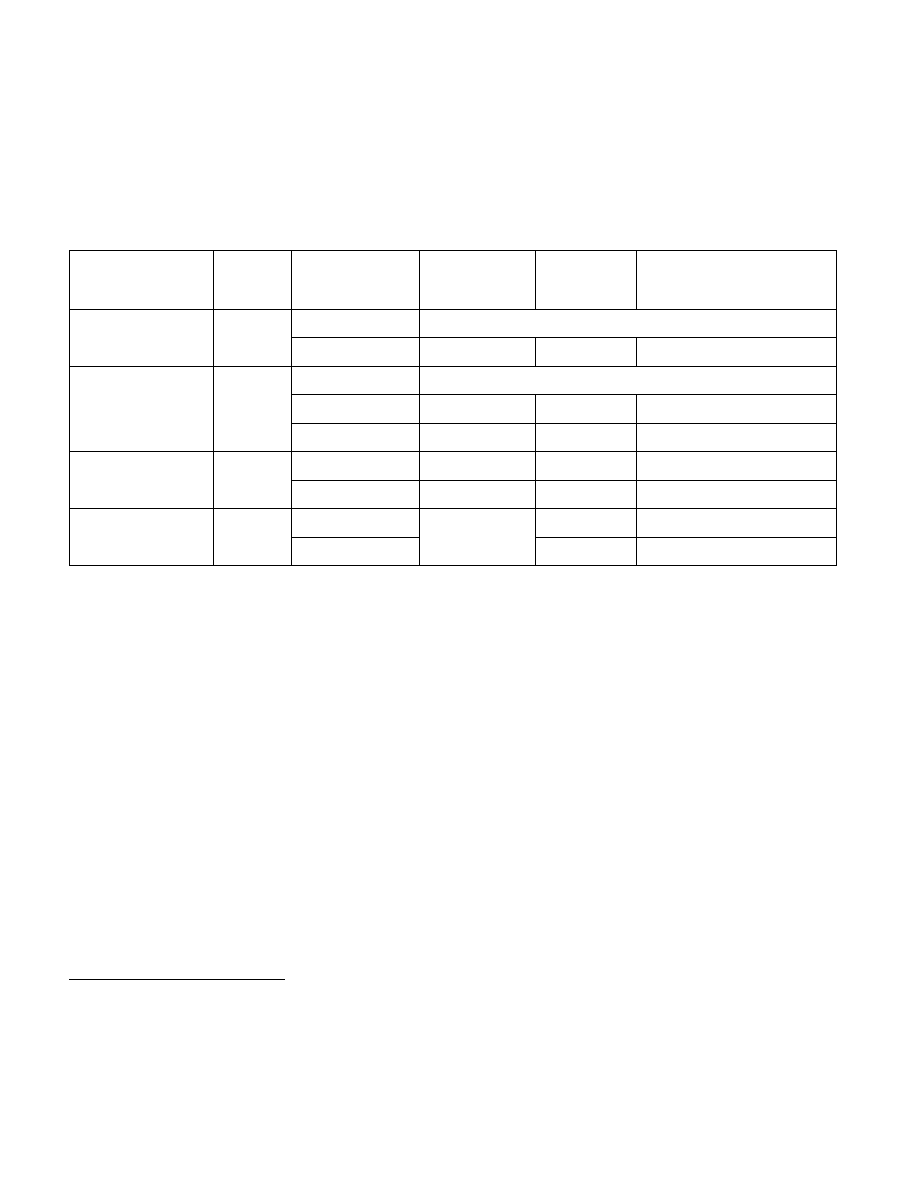

Paging structures are given different names based on their uses in the translation process. Table 4-2 gives the

names of the different paging structures. It also provides, for each structure, the source of the physical address

used to locate it (CR3 or a different paging-structure entry); the bits in the linear address used to select an entry

from the structure; and details of whether and how such an entry can map a page.

4.3 32-BIT

PAGING

A logical processor uses 32-bit paging if CR0.PG = 1 and CR4.PAE = 0. 32-bit paging translates 32-bit linear

addresses to 40-bit physical addresses.

1

Although 40 bits corresponds to 1 TByte, linear addresses are limited to

32 bits; at most 4 GBytes of linear-address space may be accessed at any given time.

32-bit paging uses a hierarchy of paging structures to produce a translation for a linear address. CR3 is used to

locate the first paging-structure, the page directory. Table 4-3 illustrates how CR3 is used with 32-bit paging.

32-bit paging may map linear addresses to either 4-KByte pages or 4-MByte pages. Figure 4-2 illustrates the

translation process when it uses a 4-KByte page; Figure 4-3 covers the case of a 4-MByte page. The following

items describe the 32-bit paging process in more detail as well has how the page size is determined:

•

A 4-KByte naturally aligned page directory is located at the physical address specified in bits 31:12 of CR3 (see

Table 4-3). A page directory comprises 1024 32-bit entries (PDEs). A PDE is selected using the physical address

defined as follows:

— Bits 39:32 are all 0.

— Bits 31:12 are from CR3.

Table 4-2. Paging Structures in the Different Paging Modes

Paging Structure

Entry

Name

Paging Mode

Physical

Address of

Structure

Bits Selecting

Entry

Page Mapping

PML4 table

PML4E

32-bit, PAE

N/A

IA-32e

CR3

47:39

N/A (PS must be 0)

Page-directory-

pointer table

PDPTE

32-bit

N/A

PAE

CR3

31:30

N/A (PS must be 0)

IA-32e

PML4E

38:30

1-GByte page if PS=1

1

NOTES:

1. Not all processors allow the PS flag to be 1 in PDPTEs; see Section 4.1.4 for how to determine whether 1-GByte pages are supported.

Page directory

PDE

32-bit

CR3

31:22

4-MByte page if PS=1

2

2. 32-bit paging ignores the PS flag in a PDE (and uses the entry to reference a page table) unless CR4.PSE = 1. Not all processors allow

CR4.PSE to be 1; see Section 4.1.4 for how to determine whether 4-MByte pages are supported with 32-bit paging.

PAE, IA-32e

PDPTE

29:21

2-MByte page if PS=1

Page table

PTE

32-bit

PDE

21:12

4-KByte page

PAE, IA-32e

20:12

4-KByte page

1. Bits in the range 39:32 are 0 in any physical address used by 32-bit paging except those used to map 4-MByte pages. If the proces-

sor does not support the PSE-36 mechanism, this is true also for physical addresses used to map 4-MByte pages. If the processor

does support the PSE-36 mechanism and MAXPHYADDR < 40, bits in the range 39:MAXPHYADDR are 0 in any physical address used

to map a 4-MByte page. (The corresponding bits are reserved in PDEs.) See Section 4.1.4 for how to determine MAXPHYADDR and

whether the PSE-36 mechanism is supported.