18-106 Vol. 3B

PERFORMANCE MONITORING

•

IA32_PERF_CAPABILITIES.PEBSArchRegs[7]: Indicator of PEBS assist save architectural registers, see Section

18.4.4.2.

•

IA32_PERF_CAPABILITIES.PEBS_FMT[bits 11:8]: Specifies the encoding of the layout of PEBS records, see

Section 18.4.4.2.

•

IA32_PERF_CAPABILITIES.SMM_FRZ[12]: Indicates IA32_DEBUGCTL.FREEZE_WHILE_SMM is supported if 1,

see Section 18.18.1.

•

IA32_PERF_CAPABILITIES.FULL_WRITE[13]: Indicates the processor supports IA32_A_PMCx interface for

updating bits 32 and above of IA32_PMCx, see Section 18.2.5.

18.18.1 Filtering of SMM Handler Overhead

When performance monitoring facilities and/or branch profiling facilities (see Section 17.5, “Last Branch, Interrupt,

and Exception Recording (Intel® Core™ 2 Duo and Intel® Atom™ Processors)”) are enabled, these facilities

capture event counts, branch records and branch trace messages occurring in a logical processor. The occurrence

of interrupts, instruction streams due to various interrupt handlers all contribute to the results recorded by these

facilities.

If CPUID.01H:ECX.PDCM[bit 15] is 1, the processor supports the IA32_PERF_CAPABILITIES MSR. If

IA32_PERF_CAPABILITIES.FREEZE_WHILE_SMM[Bit 12] is 1, the processor supports the ability for system soft-

ware using performance monitoring and/or branch profiling facilities to filter out the effects of servicing system

management interrupts.

If the FREEZE_WHILE_SMM capability is enabled on a logical processor and after an SMI is delivered, the processor

will clear all the enable bits of IA32_PERF_GLOBAL_CTRL, save a copy of the content of IA32_DEBUGCTL and

disable LBR, BTF, TR, and BTS fields of IA32_DEBUGCTL before transferring control to the SMI handler.

The enable bits of IA32_PERF_GLOBAL_CTRL will be set to 1, the saved copy of IA32_DEBUGCTL prior to SMI

delivery will be restored , after the SMI handler issues RSM to complete its servicing.

It is the responsibility of the SMM code to ensure the state of the performance monitoring and branch profiling facil-

ities are preserved upon entry or until prior to exiting the SMM. If any of this state is modified due to actions by the

SMM code, the SMM code is required to restore such state to the values present at entry to the SMM handler.

System software is allowed to set IA32_DEBUGCTL.FREEZE_WHILE_SMM_EN[bit 14] to 1 only supported as indi-

cated by IA32_PERF_CAPABILITIES.FREEZE_WHILE_SMM[Bit 12] reporting 1.

18.19 PERFORMANCE MONITORING AND DUAL-CORE TECHNOLOGY

The performance monitoring capability of dual-core processors duplicates the microarchitectural resources of a

single-core processor implementation. Each processor core has dedicated performance monitoring resources.

In the case of Pentium D processor, each logical processor is associated with dedicated resources for performance

monitoring. In the case of Pentium processor Extreme edition, each processor core has dedicated resources, but

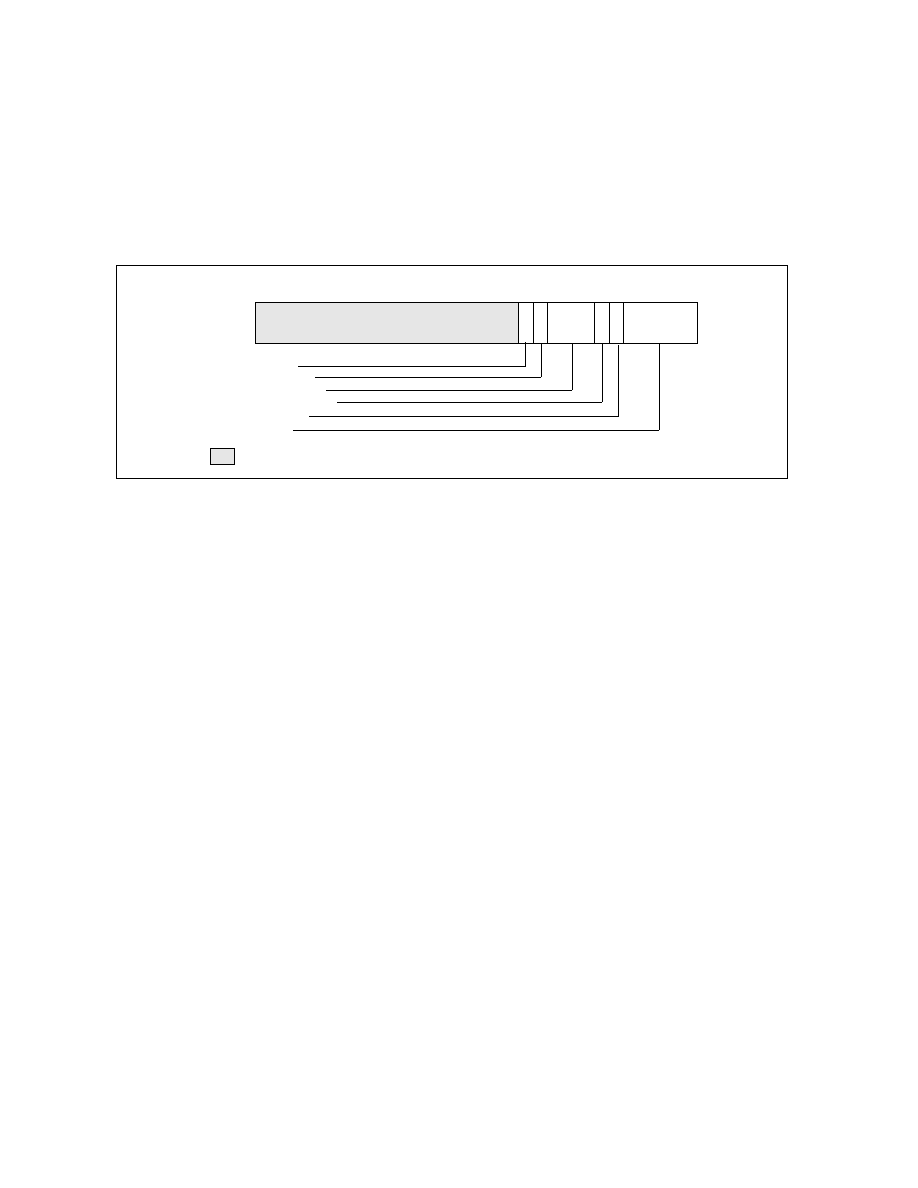

Figure 18-49. Layout of IA32_PERF_CAPABILITIES MSR

SMM_FREEZE (R/O)

PEBS_REC_FMT (R/O)

8 7

0

12

3

1

Reserved

63

2

4

11

5

6

PEBS_TRAP (R/O)

LBR_FMT (R/O)

PEBS_ARCH_REG (R/O)

13

FW_WRITE (R/O)