18-14 Vol. 3B

PERFORMANCE MONITORING

The IA32_PERF_GLOBAL_INUSE MSR provides an “InUse” bit for each programmable performance counter and

fixed counter in the processor. Additionally, it includes an indicator if the PMI mechanism has been configured by a

profiling agent.

•

IA32_PERF_GLOBAL_INUSE.PERFEVTSEL0_InUse[bit 0]: This bit reflects the logical state of

(IA32_PERFEVTSEL0[7:0] != 0).

•

IA32_PERF_GLOBAL_INUSE.PERFEVTSEL1_InUse[bit 1]: This bit reflects the logical state of

(IA32_PERFEVTSEL1[7:0] != 0).

•

IA32_PERF_GLOBAL_INUSE.PERFEVTSEL2_InUse[bit 2]: This bit reflects the logical state of

(IA32_PERFEVTSEL2[7:0] != 0).

•

IA32_PERF_GLOBAL_INUSE.PERFEVTSELn_InUse[bit n]: This bit reflects the logical state of

(IA32_PERFEVTSELn[7:0] != 0), n < CPUID.0AH:EAX[15:8].

•

IA32_PERF_GLOBAL_INUSE.FC0_InUse[bit 32]: This bit reflects the logical state of

(IA32_FIXED_CTR_CTRL[1:0] != 0).

•

IA32_PERF_GLOBAL_INUSE.FC1_InUse[bit 33]: This bit reflects the logical state of

(IA32_FIXED_CTR_CTRL[5:4] != 0).

•

IA32_PERF_GLOBAL_INUSE.FC2_InUse[bit 34]: This bit reflects the logical state of

(IA32_FIXED_CTR_CTRL[9:8] != 0).

•

IA32_PERF_GLOBAL_INUSE.PMI_InUse[bit 32]: This bit is set if any one of the following bit is set:

— IA32_PERFEVTSELn.INT[bit 20], n < CPUID.0AH:EAX[15:8];

— IA32_FIXED_CTR_CTRL.ENi_PMI, i = 0, 1, 2;

— IA32_PEBS_ENABLES.EN_PMCi, i = 0, 1, 2, 3

18.2.5

Full-Width Writes to Performance Counter Registers

The general-purpose performance counter registers IA32_PMCx are writable via WRMSR instruction. However, the

value written into IA32_PMCx by WRMSR is the signed extended 64-bit value of the EAX[31:0] input of WRMSR.

A processor that supports full-width writes to the general-purpose performance counters enumerated by

CPUID.0AH:EAX[15:8] will set IA32_PERF_CAPABILITIES[13] to enumerate its full-width-write capability See

Figure 18-49.

If IA32_PERF_CAPABILITIES.FW_WRITE[bit 13] =1, each IA32_PMCi is accompanied by a corresponding alias

address starting at 4C1H for IA32_A_PMC0.

The bit width of the performance monitoring counters is specified in CPUID.0AH:EAX[23:16].

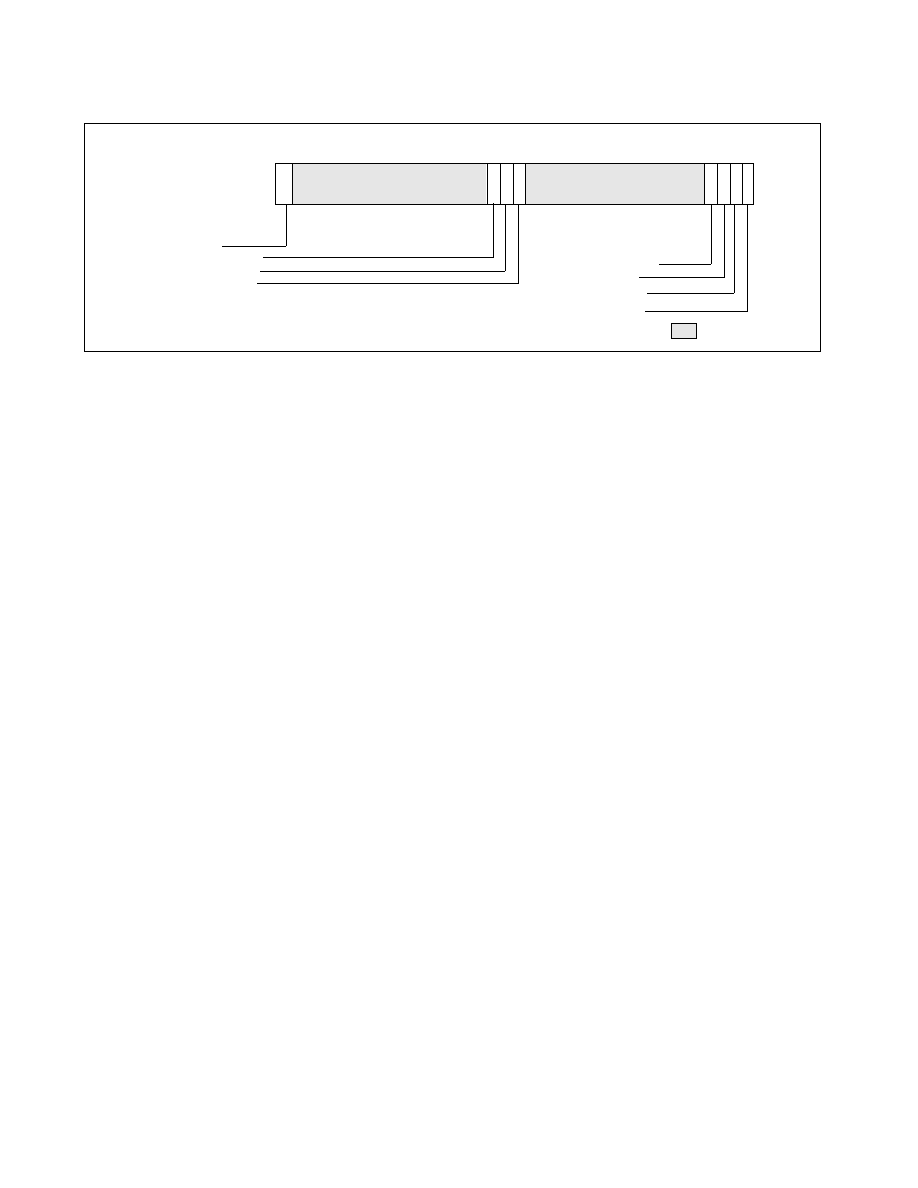

Figure 18-13. IA32_PERF_GLOBAL_INUSE MSR and Architectural Perfmon Version 4

Reserved

PMI InUse

FIXED_CTR2 InUse

FIXED_CTR1 InUse

.. 1 0

PERFEVTSEL0 InUse

31

32

33

34

35

63

..

N

....................... InUse

PERFEVTSEL(N-1) InUse

PERFEVTSEL1 InUse

FIXED_CTR0 InUse

N = CPUID.0AH:EAX[15:8]