18-70 Vol. 3B

PERFORMANCE MONITORING

•

IN_TX (bit 32): When set, the counter will only include counts that occurred inside a transactional region,

regardless of whether that region was aborted or committed. This bit may only be set if the processor supports

HLE or RTM.

•

IN_TXCP (bit 33): When set, the counter will not include counts that occurred inside of an aborted transac-

tional region. This bit may only be set if the processor supports HLE or RTM. This bit may only be set for

IA32_PERFEVTSEL2.

When the IA32_PERFEVTSELx MSR is programmed with both IN_TX=0 and IN_TXCP=0 on a processor that

supports Intel TSX, the result in a counter may include detectable conditions associated with a transaction code

region for its aborted execution (if any) and completed execution.

In the initial implementation, software may need to take pre-caution when using the IN_TXCP bit. see Table 35-27.

A common usage of setting IN_TXCP=1 is to capture the number of events that were discarded due to a transac-

tional abort. With IA32_PMC2 configured to count in such a manner, then when a transactional region aborts, the

value for that counter is restored to the value it had prior to the aborted transactional region. As a result, any

updates performed to the counter during the aborted transactional region are discarded.

On the other hand, setting IN_TX=1 can be used to drill down on the performance characteristics of transactional

code regions. When a PMCx is configured with the corresponding IA32_PERFEVTSELx.IN_TX=1, only eventing

conditions that occur inside transactional code regions are propagated to the event logic and reflected in the

counter result. Eventing conditions specified by IA32_PERFEVTSELx but occurring outside a transactional region

are discarded. The following example illustrates using three counters to drill down cycles spent inside and outside

of transactional regions:

•

Program IA32_PERFEVTSEL2 to count Unhalted_Core_Cycles with (IN_TXCP=1, IN_TX=0), such that

IA32_PMC2 will count cycles spent due to aborted TSX transactions;

•

Program IA32_PERFEVTSEL0 to count Unhalted_Core_Cycles with (IN_TXCP=0, IN_TX=1), such that

IA32_PMC0 will count cycles spent by the transactional code regions;

•

Program IA32_PERFEVTSEL1 to count Unhalted_Core_Cycles with (IN_TXCP=0, IN_TX=0), such that

IA32_PMC1 will count total cycles spent by the non-transactional code and transactional code regions.

Additionally, a number of performance events are solely focused on characterizing the execution of Intel TSX trans-

actional code, they are listed in Table 19-8.

18.11.5.1 Intel TSX and PEBS Support

If a PEBS event would have occurred inside a transactional region, then the transactional region first aborts, and

then the PEBS event is processed.

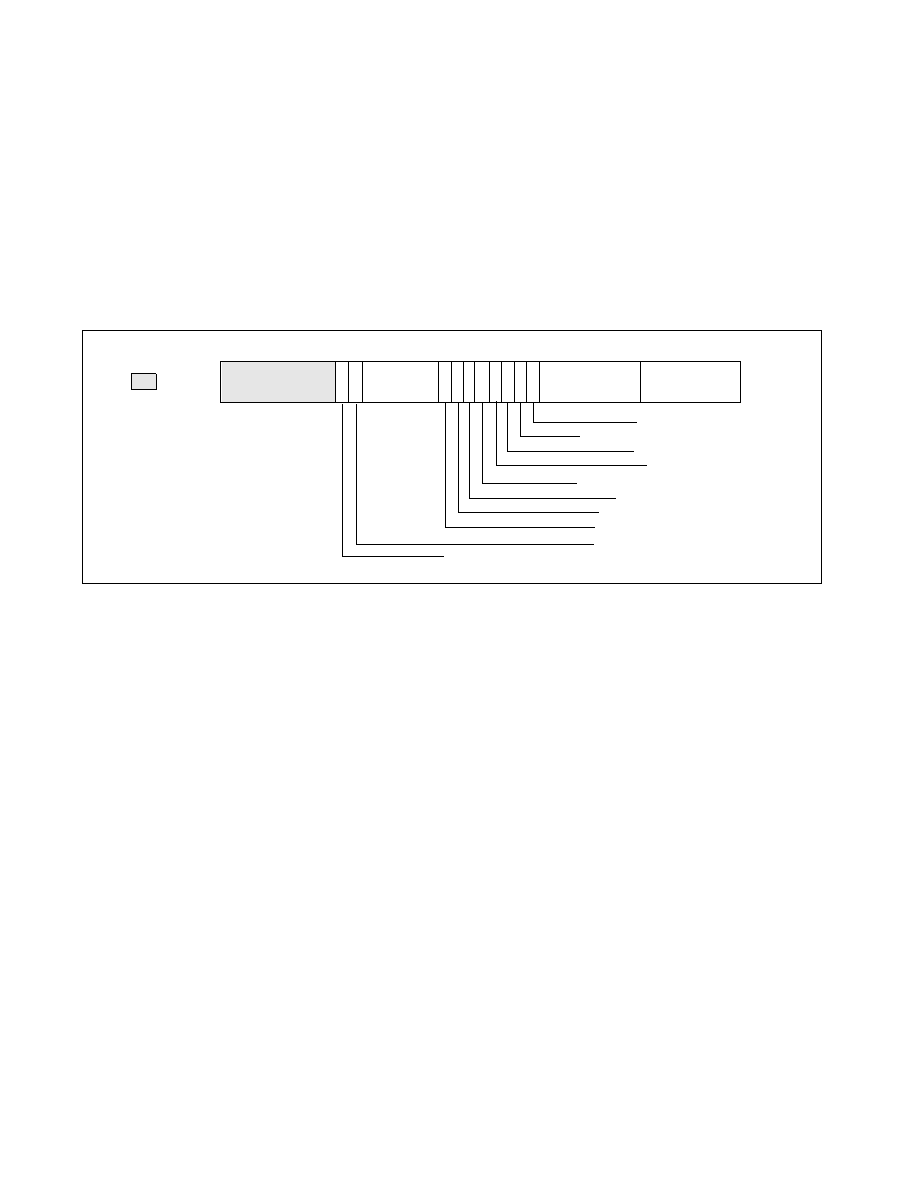

Figure 18-40. Layout of IA32_PERFEVTSELx MSRs Supporting Intel TSX

31

INV—Invert counter mask

EN—Enable counters

INT—APIC interrupt enable

PC—Pin control

8 7

0

Event Select

E—Edge detect

OS—Operating system mode

USR—User Mode

Counter Mask

E

E

N

I

N

T

19

16

18

15

17

20

21

22

23

24

Reserved

I

N

V

P

C

U

S

R

O

S

Unit Mask (UMASK)

(CMASK)

63

ANY—Any Thread

A

N

Y

34

IN_TX—In Trans. Rgn

IN_TXCP—In Tx exclude abort (PERFEVTSEL2 Only)