Vol. 3B 18-73

PERFORMANCE MONITORING

Details of Intel Processor Trace is described in Chapter 36, ‚ÄúIntel¬ģ Processor Trace‚ÄĚ.

IA32_PERF_GLOBAL_OVF_CTRL MSR provide a corresponding reset control bit.

The specifics of non-architectural performance events are listed in Chapter 19, ‚ÄúPerformance Monitoring Events‚ÄĚ.

18.13 6TH

GENERATION

INTEL

¬ģ

CORE

‚ĄĘ

PROCESSOR PERFORMANCE

MONITORING FACILITY

The 6th generation Intel

¬ģ

Core‚ĄĘ processor is based on the Skylake microarchitecture. The core PMU supports

architectural performance monitoring capability with version ID 4 (see Section 18.2.4) and a host of non-architec-

tural monitoring capabilities.

Architectural performance monitoring version 4 capabilities are described in Section 18.2.4.

The core PMU’s capability is similar to those described in Section 18.9 through Section 18.9.5, with some differ-

ences and enhancements summarized in Table 18-42. Additionally, the core PMU provides some enhancement to

support performance monitoring when the target workload contains instruction streams using Intel

¬ģ

Transactional

Synchronization Extensions (TSX), see

Section 18.11.5. For details of Intel TSX, see Chapter 16, “Programming with

Intel¬ģ Transactional Synchronization Extensions‚ÄĚ of Intel¬ģ 64 and IA-32 Architectures Software Developer‚Äôs

Manual, Volume 1.

Performance monitoring result may be affected by side-band activity on processors that support Intel SGX, details

are described in Chapter 43, ‚ÄúEnclave Code Debug and Profiling‚ÄĚ.

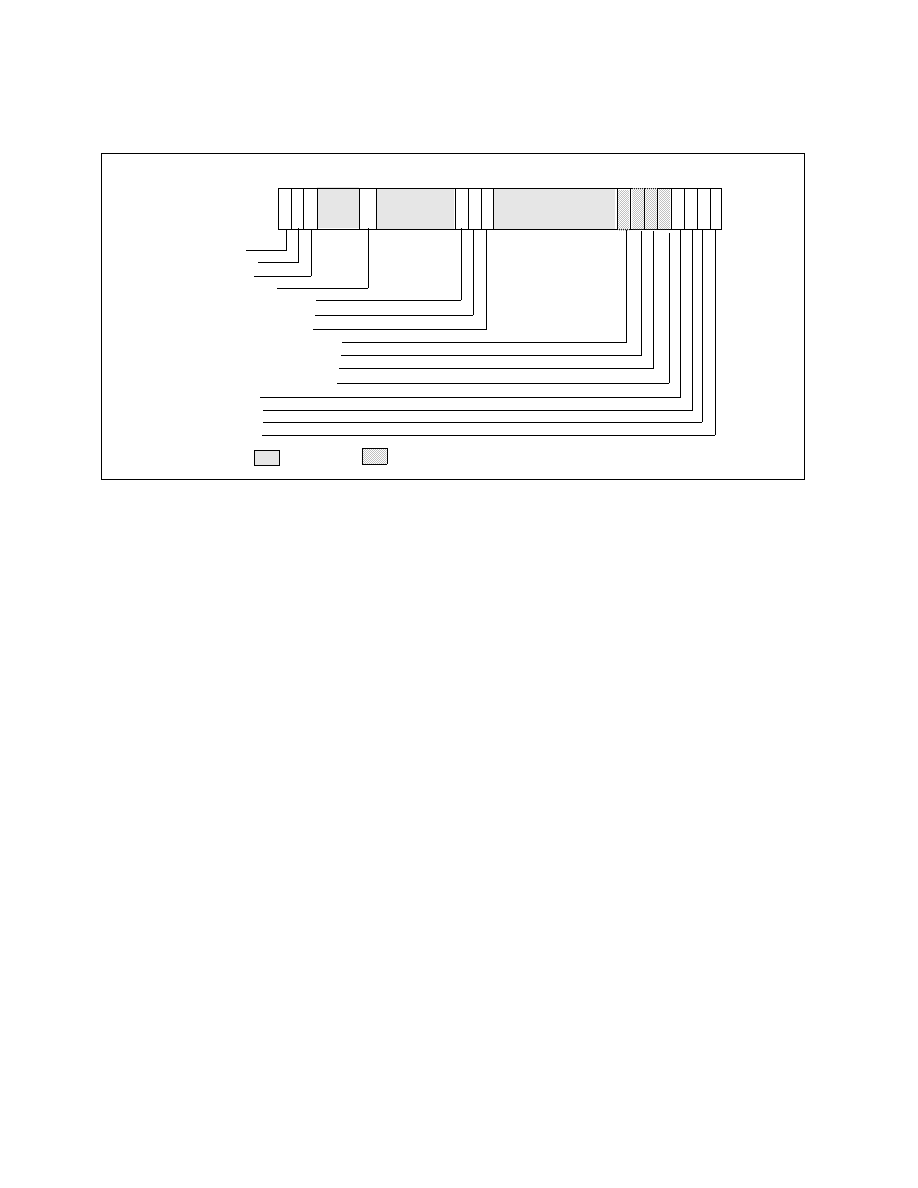

Figure 18-42. IA32_PERF_GLOBAL_OVF_CTRL MSR in Broadwell microarchitecture

62

FIXED_CTR2 ClrOverflow

FIXED_CTR1 ClrOverflow

FIXED_CTR0 ClrOverflow

PMC7_ClrOvf (if PMC7 present)

2 1 0

PMC6_ClrOvf (if PMC6 present)

31

32

33

34

35

Reserved

63

ClrCondChgd

ClrOvfDSBuffer

8 7 6 5 4 3

PMC5_ClrOvf (if PMC5 present)

PMC4_ClrOvf (if PMC4 present)

PMC3_ClrOvf

PMC2_ClrOvf

PMC1_ClrOvf

PMC0_ClrOvf

Valid if CPUID.0AH:EAX[15:8] = 8; else reserved

ClrOvfUncore

ClrTraceToPA_PMI

61

55