Vol. 3B 18-71

PERFORMANCE MONITORING

Two of the TSX performance monitoring events in Table 19-8 also support using PEBS facility to capture additional

information. They are:

•

HLE_RETIRED.ABORT ED (encoding C8H mask 04H),

•

RTM_RETIRED.ABORTED (encoding C9H mask 04H).

A transactional abort (HLE_RETIRED.ABORTED,RTM_RETIRED.ABORTED) can also be programmed to cause PEBS

events. In this scenario, a PEBS event is processed following the abort.

Pending a PEBS record inside of a transactional region will cause a transactional abort. If a PEBS record was pended

at the time of the abort or on an overflow of the TSX PEBS events listed above, only the following PEBS entries will

be valid (enumerated by PEBS entry offset B8H bits[33:32] to indicate an HLE abort or an RTM abort):

•

Offset B0H: EventingIP,

•

Offset B8H: TX Abort Information

These fields are set for all PEBS events.

•

Offset 08H (RIP/EIP) corresponds to the instruction following the outermost XACQUIRE in HLE or the first

instruction of the fallback handler of the outermost XBEGIN instruction in RTM. This is useful to identify the

aborted transactional region.

In the case of HLE, an aborted transaction will restart execution deterministically at the start of the HLE region. In

the case of RTM, an aborted transaction will transfer execution to the RTM fallback handler.

The layout of the TX Abort Information field is given in Table 18-51.

18.11.6 Uncore Performance Monitoring Facilities in the 4th Generation Intel

®

Core

™

Processors

The uncore sub-system in the 4th Generation Intel

®

Core™ processors provides its own performance monitoring

facility. The uncore PMU facility provides dedicated MSRs to select uncore performance monitoring events in a

similar manner as those described in Section 18.9.6.

The ARB unit and each C-Box provide local pairs of event select MSR and counter register. The layout of the event

select MSRs in the C-Boxes are identical as shown in Figure 18-38.

At the uncore domain level, there is a master set of control MSRs that centrally manages all the performance moni-

toring facility of uncore units. Figure 18-39 shows the layout of the uncore domain global control.

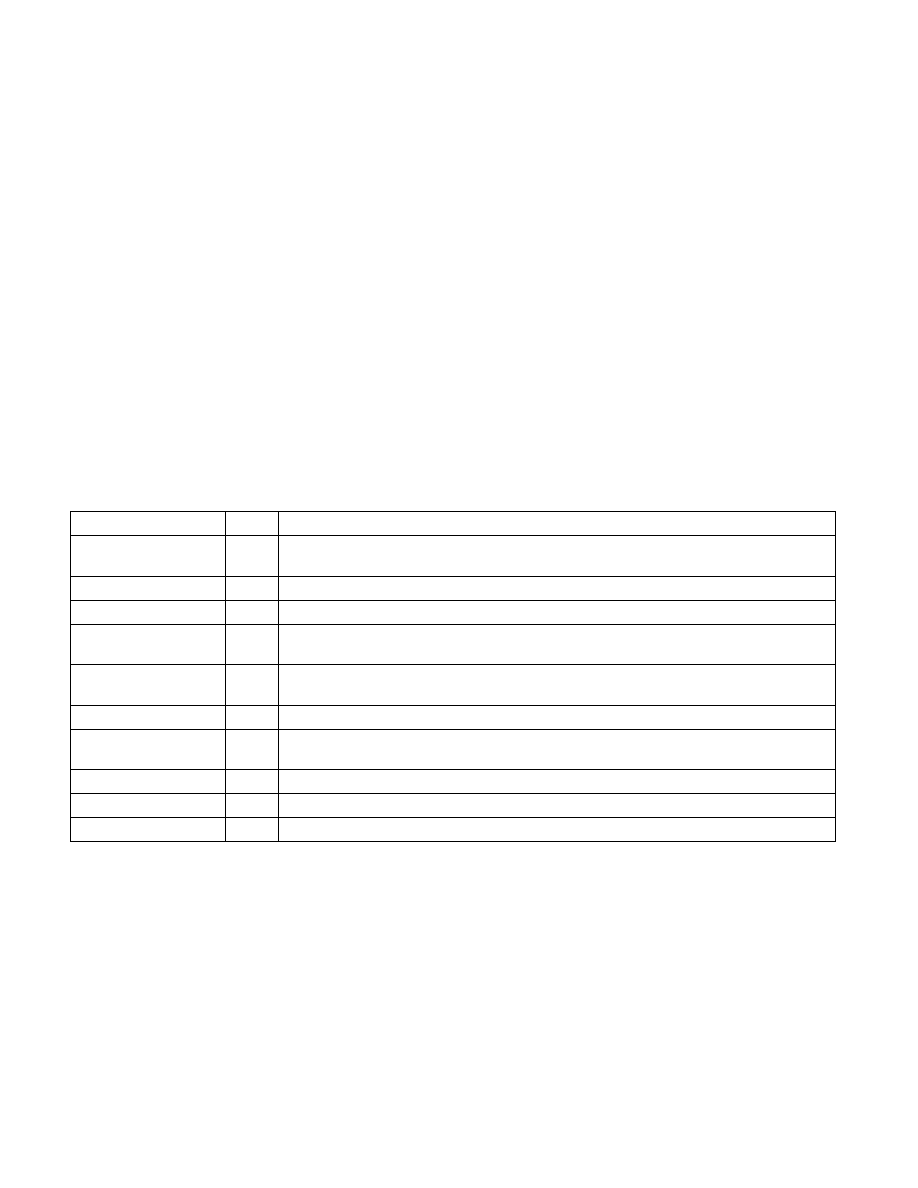

Table 18-51. TX Abort Information Field Definition

Bit Name

Offset Description

Cycles_Last_TX

31:0

The number of cycles in the last TSX region, regardless of whether that region had aborted or

committed.

HLE_Abort

32

If set, the abort information corresponds to an aborted HLE execution

RTM_Abort

33

If set, the abort information corresponds to an aborted RTM execution

Instruction_Abort

34

If set, the abort was associated with the instruction corresponding to the eventing IP (offset

0B0H) within the transactional region.

Non_Instruction_Abort

35

If set, the instruction corresponding to the eventing IP may not necessarily be related to the

transactional abort.

Retry

36

If set, retrying the transactional execution may have succeeded.

Data_Conflict

37

If set, another logical processor conflicted with a memory address that was part of the

transactional region that aborted.

Capacity Writes

38

If set, the transactional region aborted due to exceeding resources for transactional writes.

Capacity Reads

39

If set, the transactional region aborted due to exceeding resources for transactional reads.

Reserved

63:40

Reserved