18-60 Vol. 3B

PERFORMANCE MONITORING

18.9.6

Uncore Performance Monitoring Facilities In Intel

®

Core

™

i7-2xxx, Intel

®

Core

™

i5-

2xxx, Intel

®

Core

™

i3-2xxx Processor Series

The uncore sub-system in Intel

®

Core™ i7-2xxx, Intel

®

Core™ i5-2xxx, Intel

®

Core™ i3-2xxx processor series

provides a unified L3 that can support up to four processor cores. The L3 cache consists multiple slices, each slice

interface with a processor via a coherence engine, referred to as a C-Box. Each C-Box provides dedicated facility of

MSRs to select uncore performance monitoring events and each C-Box event select MSR is paired with a counter

register, similar in style as those described in Section 18.8.2.2. The ARB unit in the uncore also provides its local

performance counters and event select MSRs. The layout of the event select MSRs in the C-Boxes and the ARB unit

are shown in Figure 18-38.

Table 18-38. MSR_OFFCORE_RSP_x Snoop Info Field Definition

Subtype Bit Name

Offset Description

Snoop

Info

SNP_NONE

31

(R/W). No details on snoop-related information

SNP_NOT_NEEDED 32

(R/W). No snoop was needed to satisfy the request.

SNP_MISS

33

(R/W). A snoop was needed and it missed all snooped caches:

-For LLC Hit, ReslHitl was returned by all cores

-For LLC Miss, Rspl was returned by all sockets and data was returned from DRAM.

SNP_NO_FWD

34

(R/W). A snoop was needed and it hits in at least one snooped cache. Hit denotes a cache-

line was valid before snoop effect. This includes:

-Snoop Hit w/ Invalidation (LLC Hit, RFO)

-Snoop Hit, Left Shared (LLC Hit/Miss, IFetch/Data_RD)

-Snoop Hit w/ Invalidation and No Forward (LLC Miss, RFO Hit S)

In the LLC Miss case, data is returned from DRAM.

SNP_FWD

35

(R/W). A snoop was needed and data was forwarded from a remote socket. This includes:

-Snoop Forward Clean, Left Shared (LLC Hit/Miss, IFetch/Data_RD/RFT).

HITM

36

(R/W). A snoop was needed and it HitM-ed in local or remote cache. HitM denotes a cache-

line was in modified state before effect as a results of snoop. This includes:

-Snoop HitM w/ WB (LLC miss, IFetch/Data_RD)

-Snoop Forward Modified w/ Invalidation (LLC Hit/Miss, RFO)

-Snoop MtoS (LLC Hit, IFetch/Data_RD).

NON_DRAM

37

(R/W). Target was non-DRAM system address. This includes MMIO transactions.

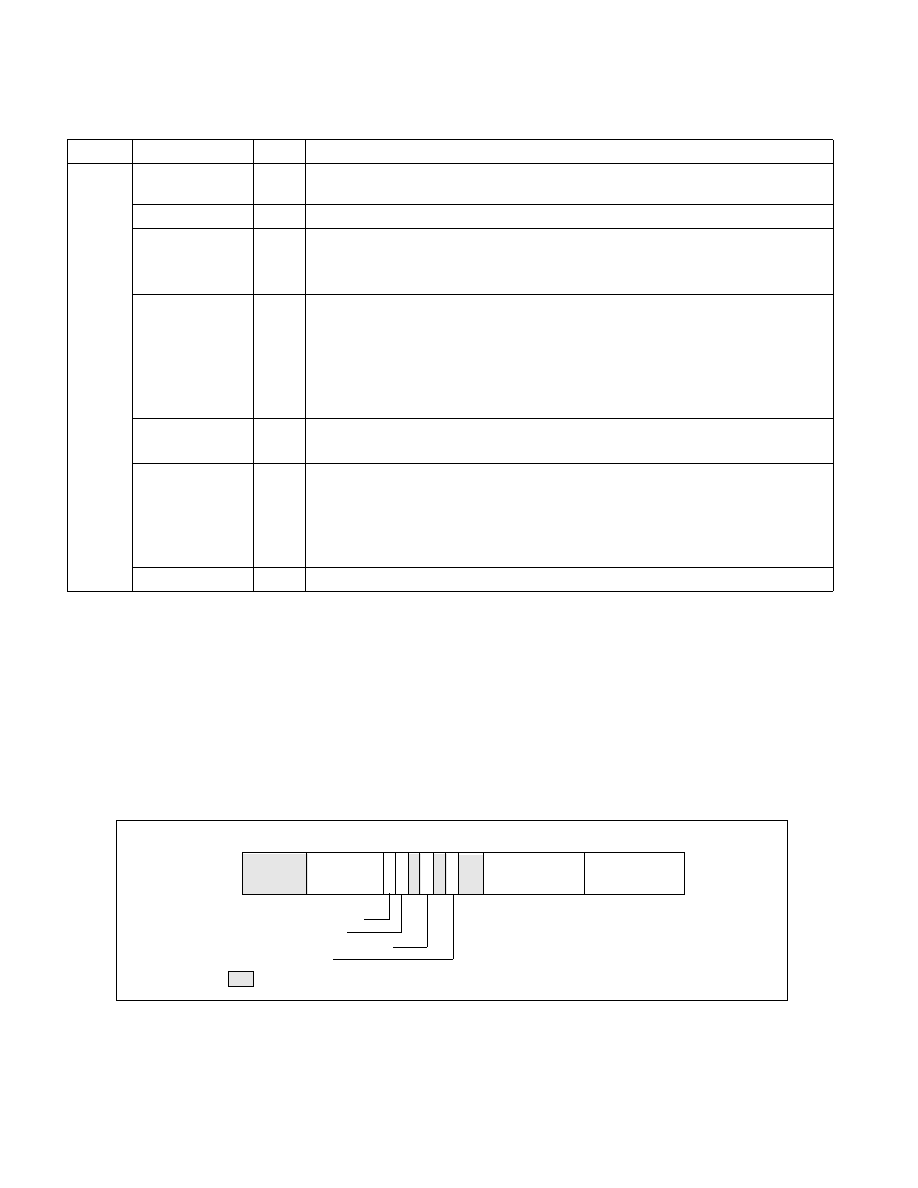

Figure 18-38. Layout of Uncore PERFEVTSEL MSR for a C-Box Unit or the ARB Unit

28

INV—Invert counter mask

EN—Enable counter

E—Edge detect

8 7

0

Event Select

Counter Mask

19

16

18

15

17

20

21

22

23

24

Reserved

Unit Mask (UMASK)

(CMASK)

63

OVF_EN—Overflow forwarding

RESET Value — 00000000_00000000H