Vol. 3B 18-61

PERFORMANCE MONITORING

The bit fields of the uncore event select MSRs for a C-box unit or the ARB unit are summarized below:

•

Event_Select (bits 7:0) and UMASK (bits 15:8): Specifies the microarchitectural condition to count in a local

uncore PMU counter, see Table 19-16.

•

E (bit 18): Enables edge detection filtering, if 1.

•

OVF_EN (bit 20): Enables the overflow indicator from the uncore counter forwarded to

MSR_UNC_PERF_GLOBAL_CTRL, if 1.

•

EN (bit 22): Enables the local counter associated with this event select MSR.

•

INV (bit 23): Event count increments with non-negative value if 0, with negated value if 1.

•

CMASK (bits 28:24): Specifies a positive threshold value to filter raw event count input.

At the uncore domain level, there is a master set of control MSRs that centrally manages all the performance moni-

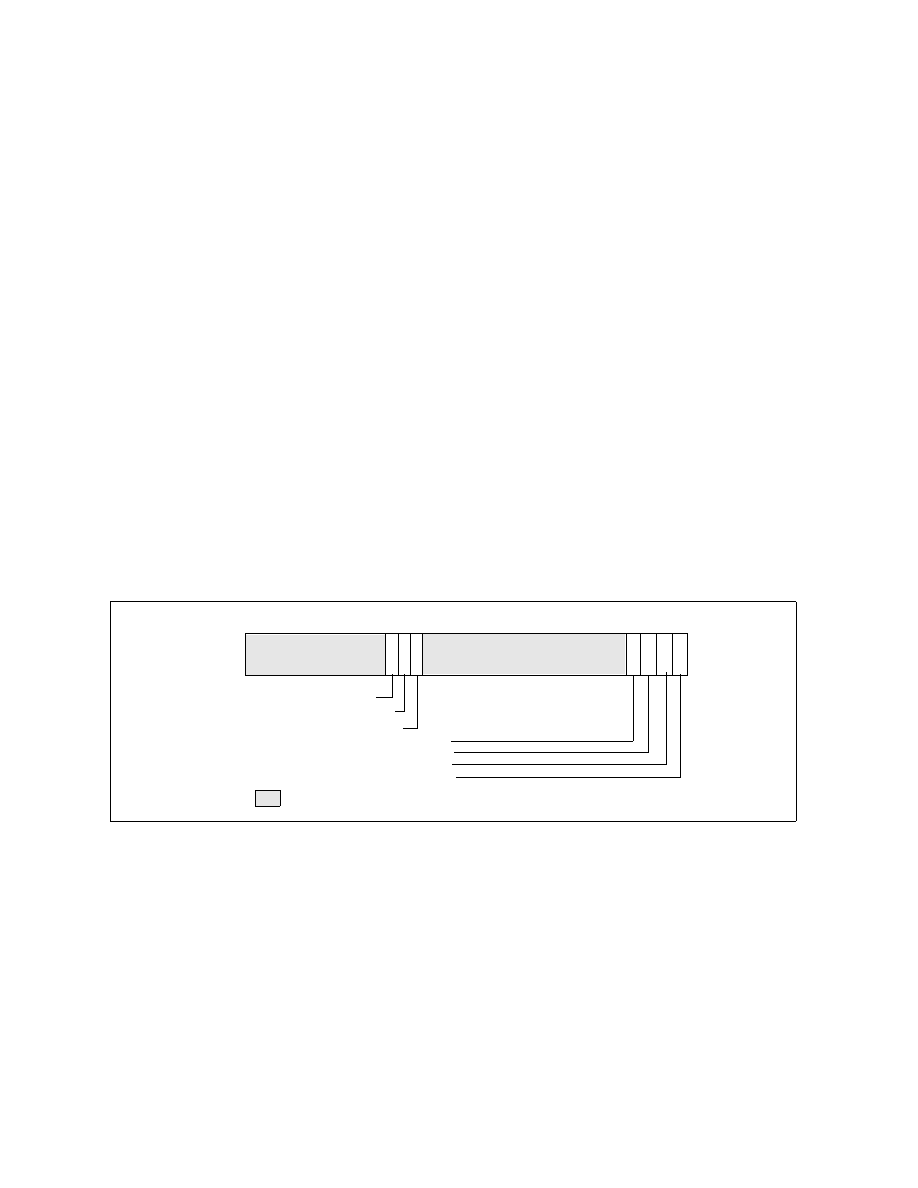

toring facility of uncore units. Figure 18-39 shows the layout of the uncore domain global control.

When an uncore counter overflows, a PMI can be routed to a processor core. Bits 3:0 of

MSR_UNC_PERF_GLOBAL_CTRL can be used to select which processor core to handle the uncore PMI. Software

must then write to bit 13 of IA32_DEBUGCTL (at address 1D9H) to enable this capability.

•

PMI_SEL_Core#: Enables the forwarding of an uncore PMI request to a processor core, if 1. If bit 30 (WakePMI)

is ‘1’, a wake request is sent to the respective processor core prior to sending the PMI.

•

EN: Enables the fixed uncore counter, the ARB counters, and the CBO counters in the uncore PMU, if 1. This bit

is cleared if bit 31 (FREEZE) is set and any enabled uncore counters overflow.

•

WakePMI: Controls sending a wake request to any halted processor core before issuing the uncore PMI request.

If a processor core was halted and not sent a wake request, the uncore PMI will not be serviced by the

processor core.

•

FREEZE: Provides the capability to freeze all uncore counters when an overflow condition occurs in a unit

counter. When this bit is set, and a counter overflow occurs, the uncore PMU logic will clear the global enable

bit (bit 29).

Figure 18-39. Layout of MSR_UNC_PERF_GLOBAL_CTRL MSR for Uncore

FREEZE—Freeze counters

EN—Enable all uncore counters

0

28

29

30

31

32

Reserved

63

WakePMI—Wake cores on PMI

RESET Value — 00000000_00000000H

4 3 2 1

PMI_Sel_Core3 — Uncore PMI to core 3

PMI_Sel_Core2 — Uncore PMI to core 2

PMI_Sel_Core1 — Uncore PMI to core 1

PMI_Sel_Core0 — Uncore PMI to core 0