Vol. 3B 18-67

PERFORMANCE MONITORING

DataLA can use any one of the IA32_PMC0-IA32_PMC3 counters. Counter overflows will initiate the generation of

PEBS records. Upon counter overflow, hardware captures the linear address and possible other status information

of the retiring memory uop. This information is then written to the PEBS record that is subsequently generated.

To enable the DataLA facility, software must complete the following steps. Please note that the DataLA facility relies

on the PEBS facility, so the PEBS configuration requirements must be completed before attempting to capture

DataLA information.

•

Complete the PEBS configuration steps.

•

Program the an event listed in Table 18-45 using any one of IA32_PERFEVTSEL0-IA32_PERFEVTSEL3.

•

Set the corresponding IA32_PEBS_ENABLE.PEBS_EN_CTRx bit. This enables the corresponding IA32_PMCx as

a PEBS counter and enables the DataLA facility.

When the DataLA facility is enabled, the relevant information written into a PEBS record affects entries at offsets

98H, A0H and A8H, as shown in Table 18-46.

18.11.3.1 EventingIP Record

The PEBS record layout for processors based on Intel microarchitecture code name Haswell adds a new field at

offset 0B0H. This is the eventingIP field that records the IP address of the retired instruction that triggered the

PEBS assist. The EIP/RIP field at offset 08H records the IP address of the next instruction to be executed following

the PEBS assist.

18.11.4 Off-core Response Performance Monitoring

The core PMU facility to collect off-core response events are similar to those described in Section 18.9.5. The event

codes are listed in Table 18-35. Each event code for off-core response monitoring requires programming an asso-

ciated configuration MSR, MSR_OFFCORE_RSP_x. Software must program MSR_OFFCORE_RSP_x according to:

•

Transaction request type encoding (bits 15:0): see Table 18-47.

•

Supplier information (bits 30:16): see Table 18-48 and Table 18-48.

•

Snoop response information (bits 37:31): see Table 18-38.

MEM_LOAD_UOPS_L3_HIT_RETIRED.XSNP_HIT

MEM_LOAD_UOPS_L3_HIT_RETIRED.XSNP_HITM

UOPS_RETIRED.ALL (if load or store is tagged)

MEM_LOAD_UOPS_LLC_HIT_RETIRED.XSNP_NONE

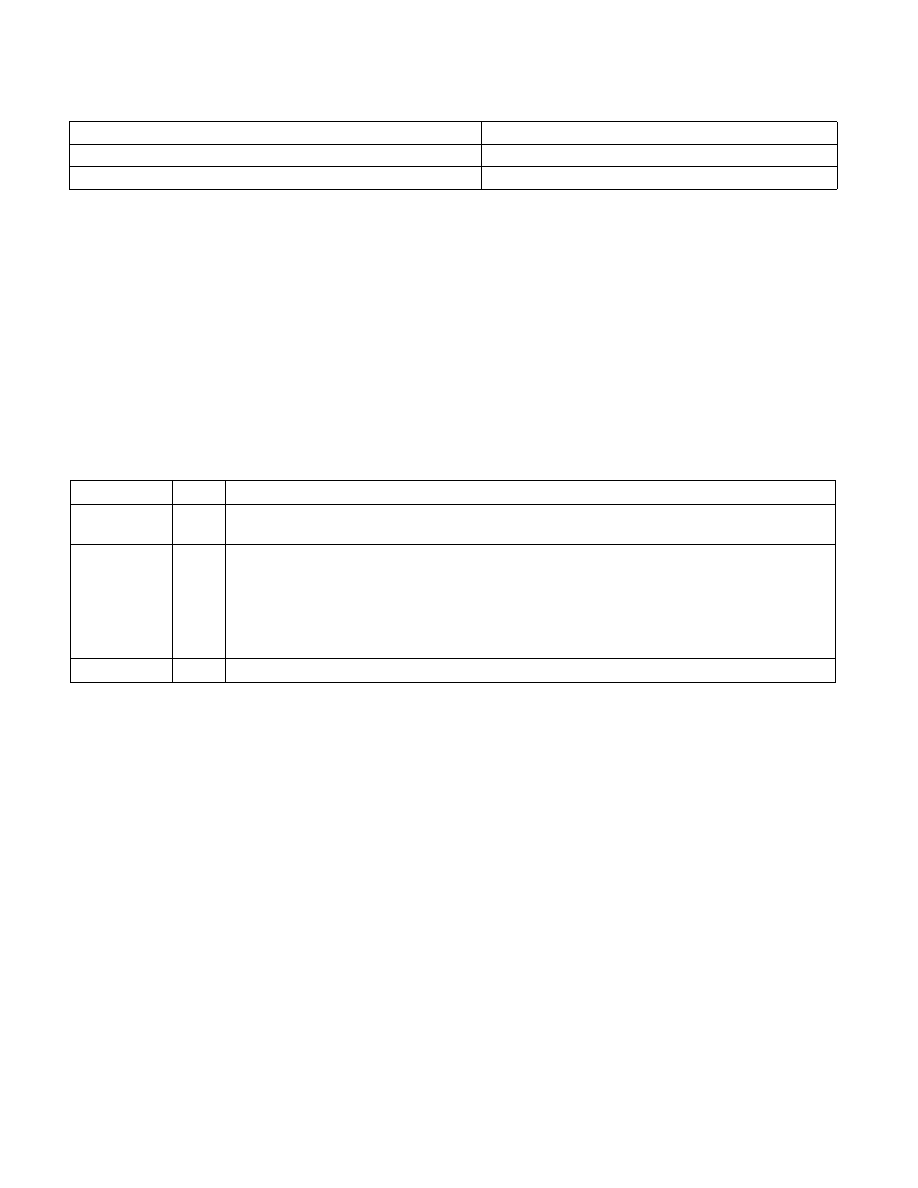

Table 18-46. Layout of Data Linear Address Information In PEBS Record

Field Offset

Description

Data Linear

Address

98H

The linear address of the load or the destination of the store.

Store Status

A0H

• DCU Hit (Bit 0): The store hit the data cache closest to the core (L1 cache) if this bit is set, otherwise

the store missed the data cache. This information is valid only for the following store events:

UOPS_RETIRED.ALL (if store is tagged),

MEM_UOPS_RETIRED.STLB_MISS_STORES,

MEM_UOPS_RETIRED.SPLIT_STORES, MEM_UOPS_RETIRED.ALL_STORES

• Other bits are zero, The STLB_MISS, LOCK bit information can be obtained by programming the

corresponding store event in Table 18-45.

Reserved

A8H

Always zero.

Table 18-45. Precise Events That Supports Data Linear Address Profiling (Contd.)

Event Name

Event Name