18-68 Vol. 3B

PERFORMANCE MONITORING

The supplier information field listed in Table 18-48 and Table 18-48. The fields vary across products (according to

CPUID signatures) and is noted in the description.

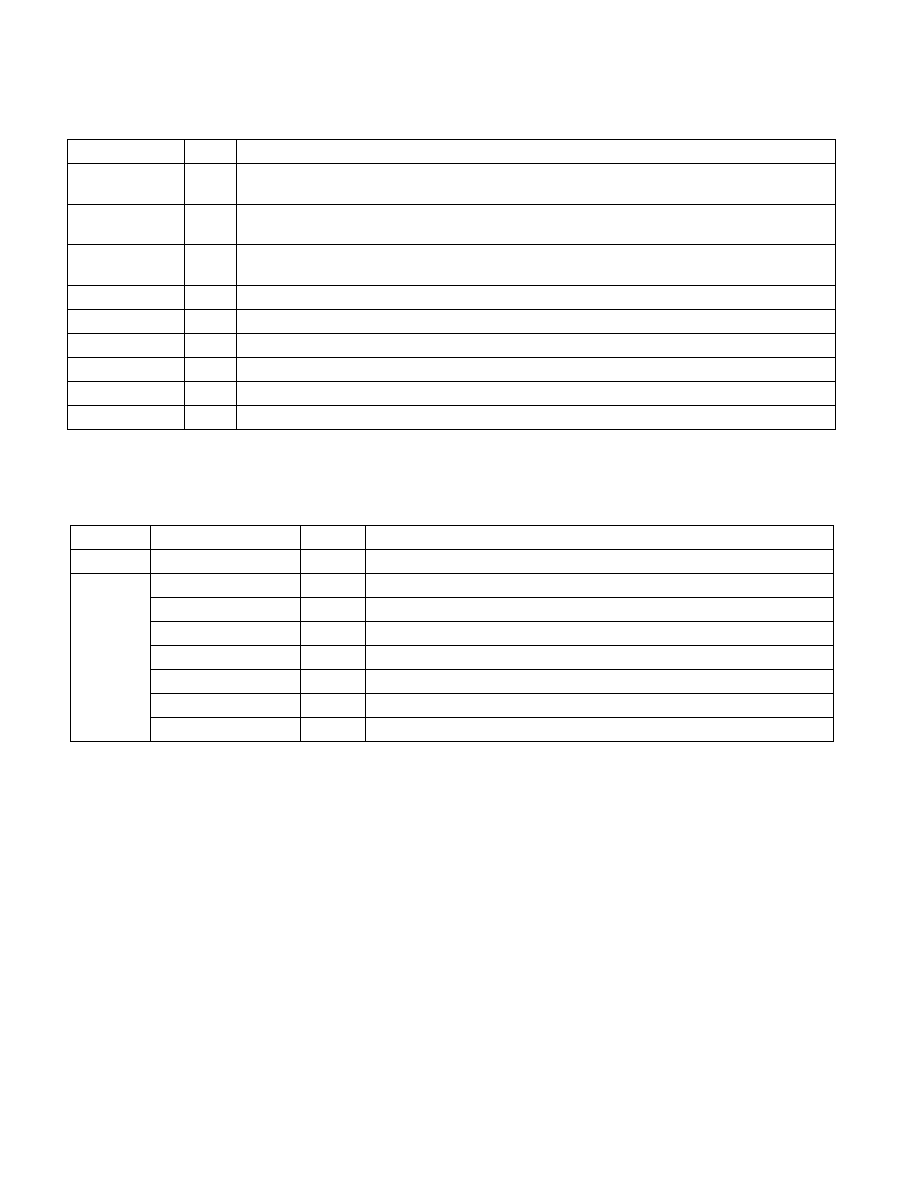

Table 18-47. MSR_OFFCORE_RSP_x Request_Type Definition (Haswell microarchitecture)

Bit Name

Offset Description

DMND_DATA_RD

0

(R/W). Counts the number of demand data reads of full and partial cachelines as well as demand data

page table entry cacheline reads. Does not count L2 data read prefetches or instruction fetches.

DMND_RFO

1

(R/W). Counts the number of demand and DCU prefetch reads for ownership (RFO) requests generated

by a write to data cacheline. Does not count L2 RFO prefetches.

DMND_IFETCH

2

(R/W). Counts the number of demand and DCU prefetch instruction cacheline reads. Does not count L2

code read prefetches.

Reserved

3

Reserved

PF_DATA_RD

4

(R/W). Counts the number of data cacheline reads generated by L2 prefetchers.

PF_RFO

5

(R/W). Counts the number of RFO requests generated by L2 prefetchers.

PF_IFETCH

6

(R/W). Counts the number of code reads generated by L2 prefetchers.

Reserved

7-14

Reserved

OTHER

15

(R/W). Any other request that crosses IDI, including I/O.

Table 18-48. MSR_OFFCORE_RSP_x Supplier Info Field Definition (CPUID Signature 06_3CH, 06_46H)

Subtype

Bit Name

Offset

Description

Common

Any

16

(R/W). Catch all value for any response types.

Supplier

Info

NO_SUPP

17

(R/W). No Supplier Information available

L3_HITM

18

(R/W). M-state initial lookup stat in L3.

L3_HITE

19

(R/W). E-state

L3_HITS

20

(R/W). S-state

Reserved

21

Reserved

LOCAL

22

(R/W). Local DRAM Controller

Reserved

30:23

Reserved