Vol. 3B 18-63

PERFORMANCE MONITORING

18.9.8 Intel

®

Xeon

®

Processor E5 Family Uncore Performance Monitoring Facility

The uncore subsystem in the Intel Xeon processor E5-2600 product family has some similarities with those of the

Intel Xeon processor E7 family. Within the uncore subsystem, localized performance counter sets are provided at

logic control unit scope. For example, each Cbox caching agent has a set of local performance counters, and the

power controller unit (PCU) has its own local performance counters. Up to 8 C-Box units are supported in the

uncore sub-system.

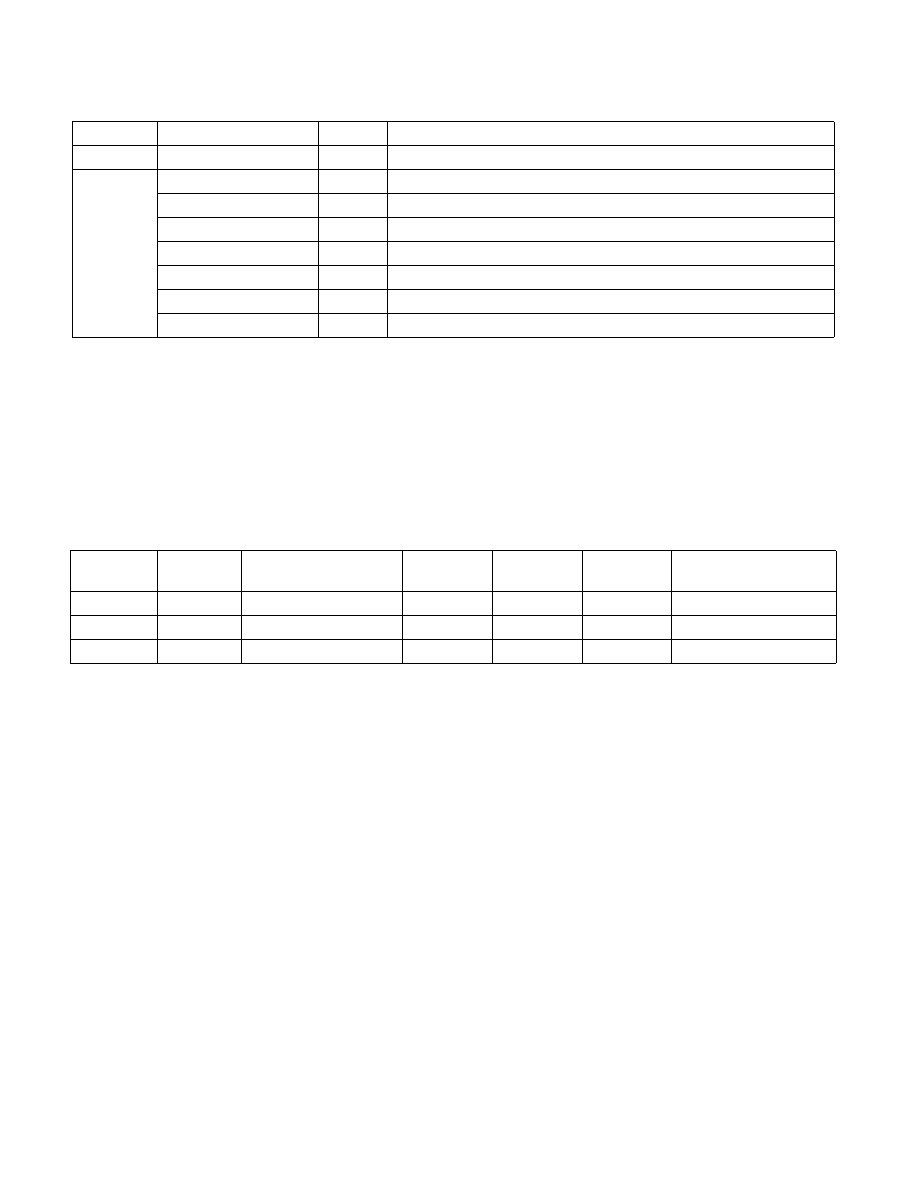

Table 18-41 summarizes the uncore PMU facilities providing MSR interfaces.

Details of the uncore performance monitoring facility of Intel Xeon Processor E5 family is available in “Intel®

Xeon® Processor E5 Uncore Performance Monitoring Programming Reference Manual”. The MSR-based uncore

PMU interfaces are listed in Table 35-22.

18.10 3RD

GENERATION

INTEL

®

CORE

™

PROCESSOR PERFORMANCE

MONITORING FACILITY

The 3rd generation Intel

®

Core™ processor family and Intel

®

Xeon

®

processor E3-1200v2 product family are

based on the Ivy Bridge microarchitecture. The performance monitoring facilities in the processor core generally

are the same as those described in Section 18.9 through Section 18.9.5. The non-architectural performance moni-

toring events supported by the processor core are listed in Table 19-14.

18.10.1 Intel

®

Xeon

®

Processor E5 v2 and E7 v2 Family Uncore Performance Monitoring

Facility

The uncore subsystem in the Intel Xeon processor E5 v2 and Intel Xeon Processor E7 v2 product families are based

on the Ivy Bridge-E microarchitecture. There are some similarities with those of the Intel Xeon processor E5 family

based on the Sandy Bridge microarchitecture. Within the uncore subsystem, localized performance counter sets

are provided at logic control unit scope.

Table 18-40. MSR_OFFCORE_RSP_x Supplier Info Field Definitions

Subtype

Bit Name

Offset

Description

Common

Any

16

(R/W). Catch all value for any response types.

Supplier Info NO_SUPP

17

(R/W). No Supplier Information available

LLC_HITM

18

(R/W). M-state initial lookup stat in L3.

LLC_HITE

19

(R/W). E-state

LLC_HITS

20

(R/W). S-state

LLC_HITF

21

(R/W). F-state

LOCAL

22

(R/W). Local DRAM Controller

Remote

30:23

(R/W): Remote DRAM Controller (either all 0s or all 1s)

Table 18-41. Uncore PMU MSR Summary for Intel® Xeon® Processor E5 Family

Box

# of Boxes

Counters per Box

Counter

Width

General

Purpose

Global

Enable Sub-control

MSRs

C-Box

8

4

44

Yes

per-box

None

PCU

1

4

48

Yes

per-box

Match/Mask

U-Box

1

2

44

Yes

uncore

None