19-52 Vol. 3B

PERFORMANCE-MONITORING EVENTS

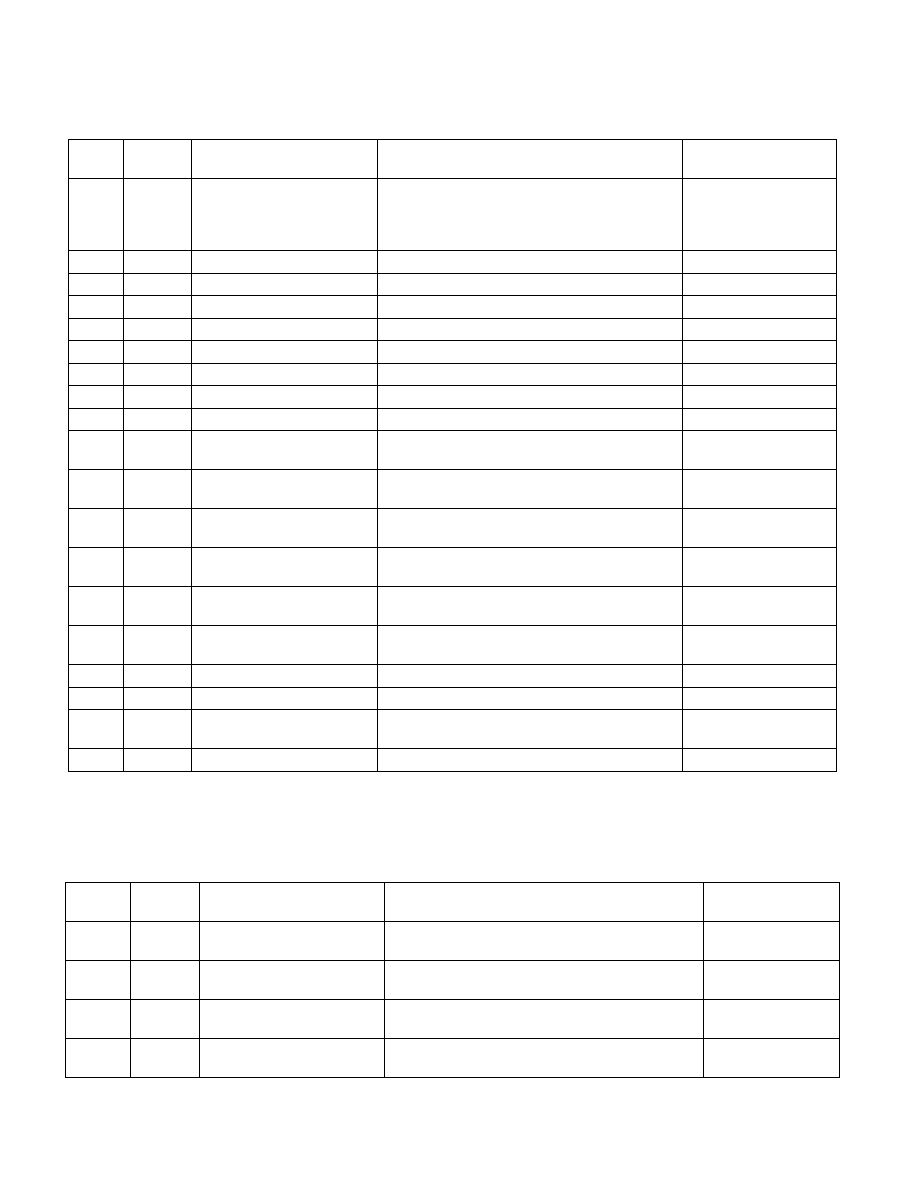

Non-architecture performance monitoring events in the processor core that are applicable only to Intel processors

with CPUID signature of DisplayFamily_DisplayModel 06_2AH are listed in Table 19-14.

E6H

01H

BACLEARS.ANY

Counts the number of times the front end is re-

steered, mainly when the BPU cannot provide a

correct prediction and this is corrected by other

branch handling mechanisms at the front end.

F0H

01H

L2_TRANS.DEMAND_DATA_RD Demand Data Read requests that access L2 cache.

F0H

02H

L2_TRANS.RFO

RFO requests that access L2 cache.

F0H

04H

L2_TRANS.CODE_RD

L2 cache accesses when fetching instructions.

F0H

08H

L2_TRANS.ALL_PF

L2 or LLC HW prefetches that access L2 cache.

Including rejects.

F0H

10H

L2_TRANS.L1D_WB

L1D writebacks that access L2 cache.

F0H

20H

L2_TRANS.L2_FILL

L2 fill requests that access L2 cache.

F0H

40H

L2_TRANS.L2_WB

L2 writebacks that access L2 cache.

F0H

80H

L2_TRANS.ALL_REQUESTS

Transactions accessing L2 pipe.

F1H

01H

L2_LINES_IN.I

L2 cache lines in I state filling L2.

Counting does not cover

rejects.

F1H

02H

L2_LINES_IN.S

L2 cache lines in S state filling L2.

Counting does not cover

rejects.

F1H

04H

L2_LINES_IN.E

L2 cache lines in E state filling L2.

Counting does not cover

rejects.

F1H

07H

L2_LINES_IN.ALL

L2 cache lines filling L2.

Counting does not cover

rejects.

F2H

01H

L2_LINES_OUT.DEMAND_CLEA

N

Clean L2 cache lines evicted by demand.

F2H

02H

L2_LINES_OUT.DEMAND_DIRT

Y

Dirty L2 cache lines evicted by demand.

F2H

04H

L2_LINES_OUT.PF_CLEAN

Clean L2 cache lines evicted by L2 prefetch.

F2H

08H

L2_LINES_OUT.PF_DIRTY

Dirty L2 cache lines evicted by L2 prefetch.

F2H

0AH

L2_LINES_OUT.DIRTY_ALL

Dirty L2 cache lines filling the L2.

Counting does not cover

rejects.

F4H

10H

SQ_MISC.SPLIT_LOCK

Split locks in SQ.

Table 19-14. Non-Architectural Performance Events applicable only to the Processor core for 2nd Generation Intel®

Core™ i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

D2H

01H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_MISS

Retired load uops which data sources were LLC hit and

cross-core snoop missed in on-pkg core cache.

Supports PEBS. PMC0-

3 only regardless HTT.

D2H

02H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_HIT

Retired load uops which data sources were LLC and

cross-core snoop hits in on-pkg core cache.

Supports PEBS.

D2H

04H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_HITM

Retired load uops which data sources were HitM

responses from shared LLC.

Supports PEBS.

D2H

08H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_NONE

Retired load uops which data sources were hits in LLC

without snoops required.

Supports PEBS.

Table 19-13. Non-Architectural Performance Events In the Processor Core Common to 2nd Generation Intel® Core™

i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series and Intel® Xeon® Processors E3 and E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment